Hello team,

My customer has a question about DDC-SCL behavior.

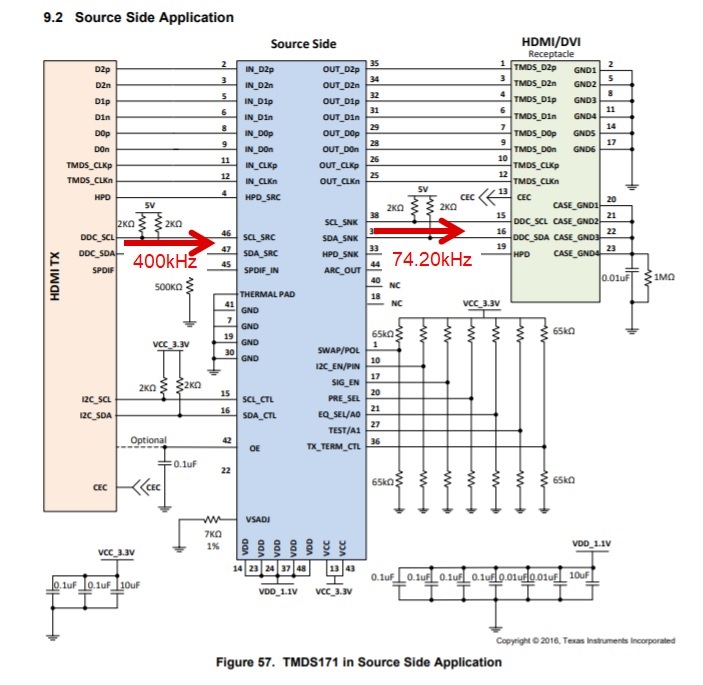

He is use TMDS171 as source side application as below. When 400kHz clock input from DDC -SCL_SRC, he saw that 74.20kHz clock from DDC -SCL_SNK. It seems that TMDS171 ACTIVE DDC BLOCK convert the lower clock frequency.

Q1) Is this correct behavior?

Q2) How does the DDC clock frequency change in ACTIVE DDC BLOCK if it is collect behavior?

Q3) Can we set DDC clock frequency if it is collect behavior?

Would you please advise?

Best Regards,

Akihisa Tamazaki