Part Number: DP83867E

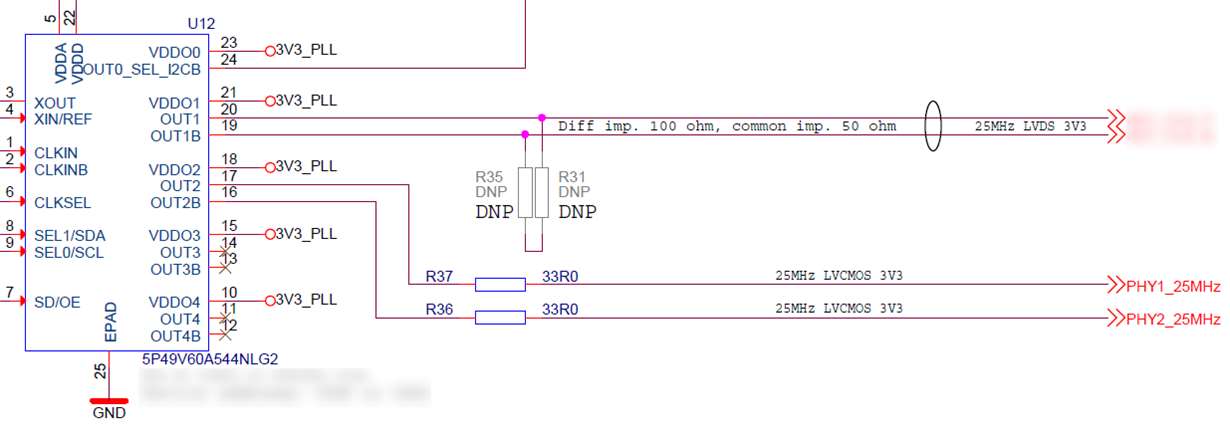

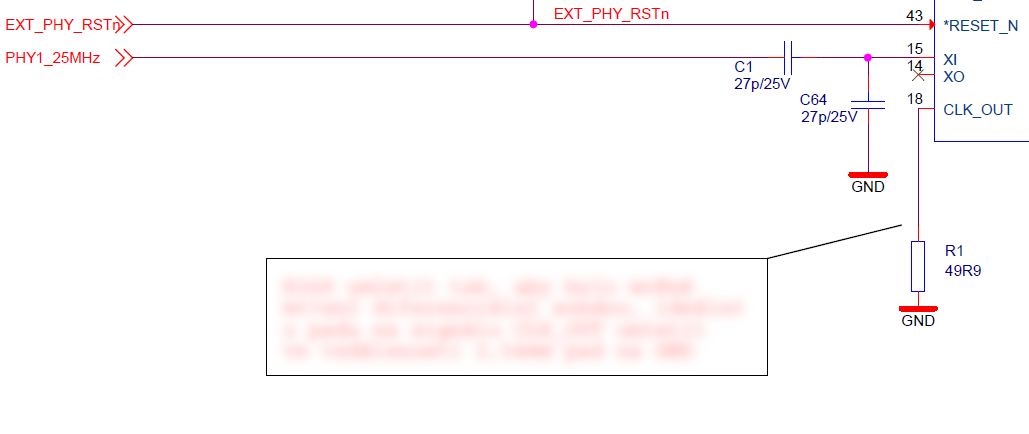

Hello, we are using DP83867ERGZT with 3.3V external oscillator connected to XI via capacitive divider as described in datasheet (Figure 28. Clock Divider).

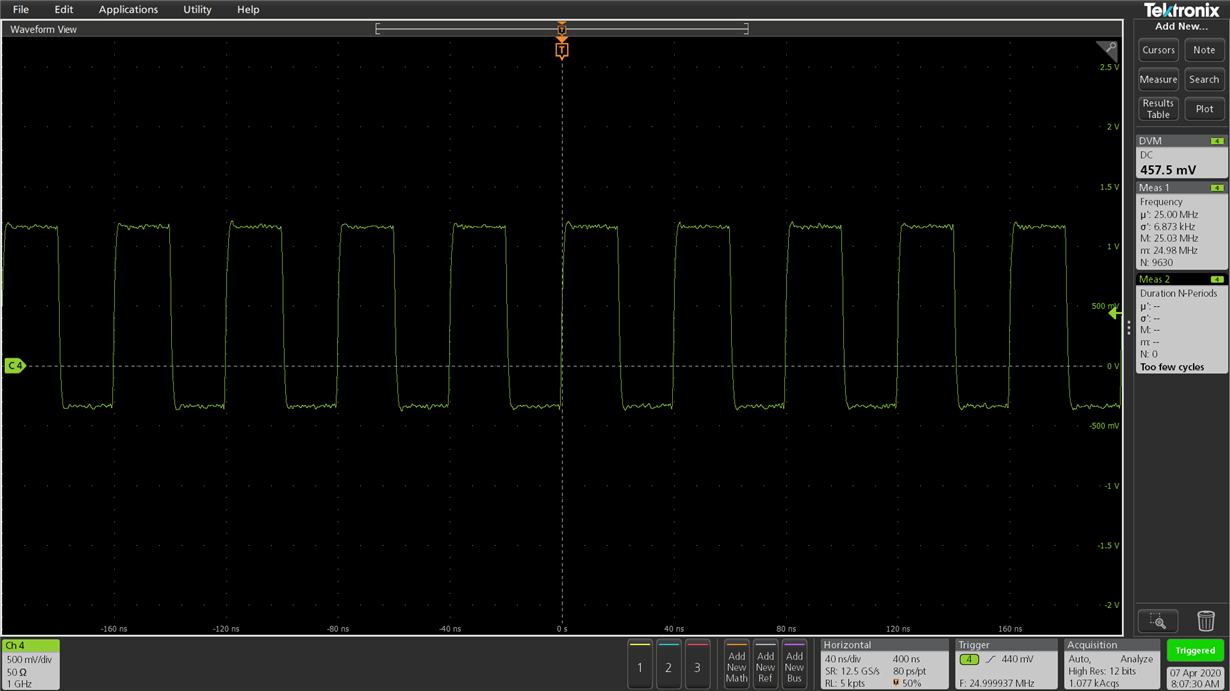

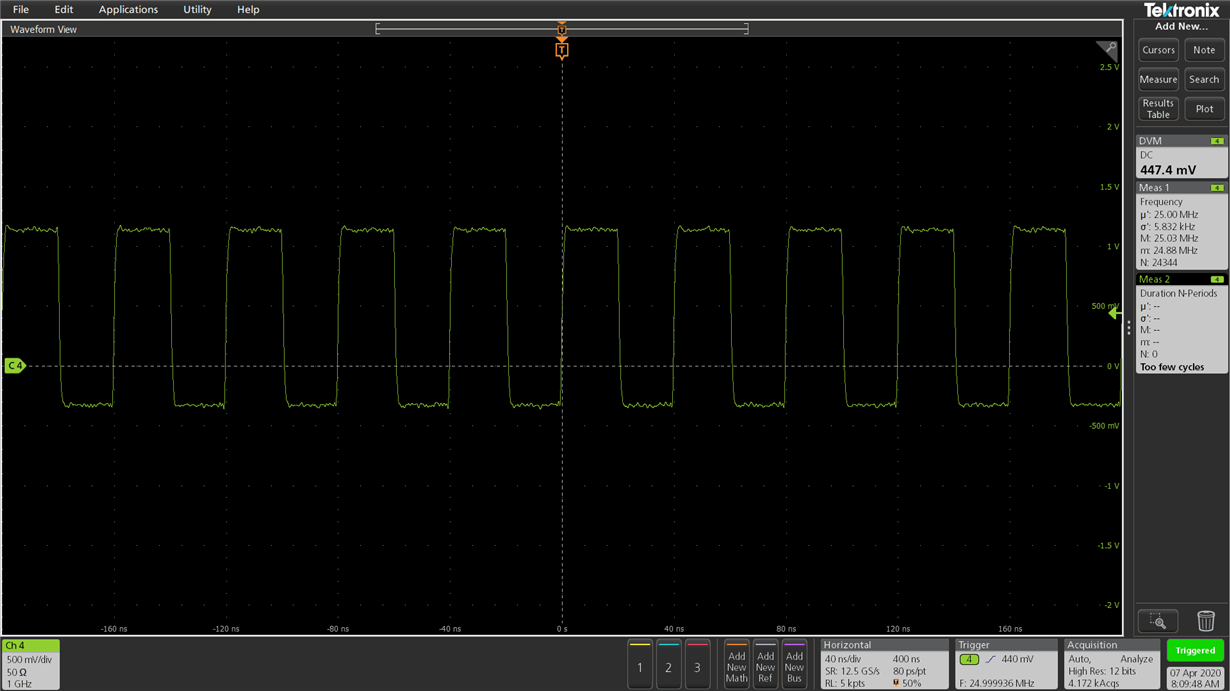

We adjusted the values of CD1/CD2 during prototype testing to meet amplitude specification defined in Electrical Characteristics.

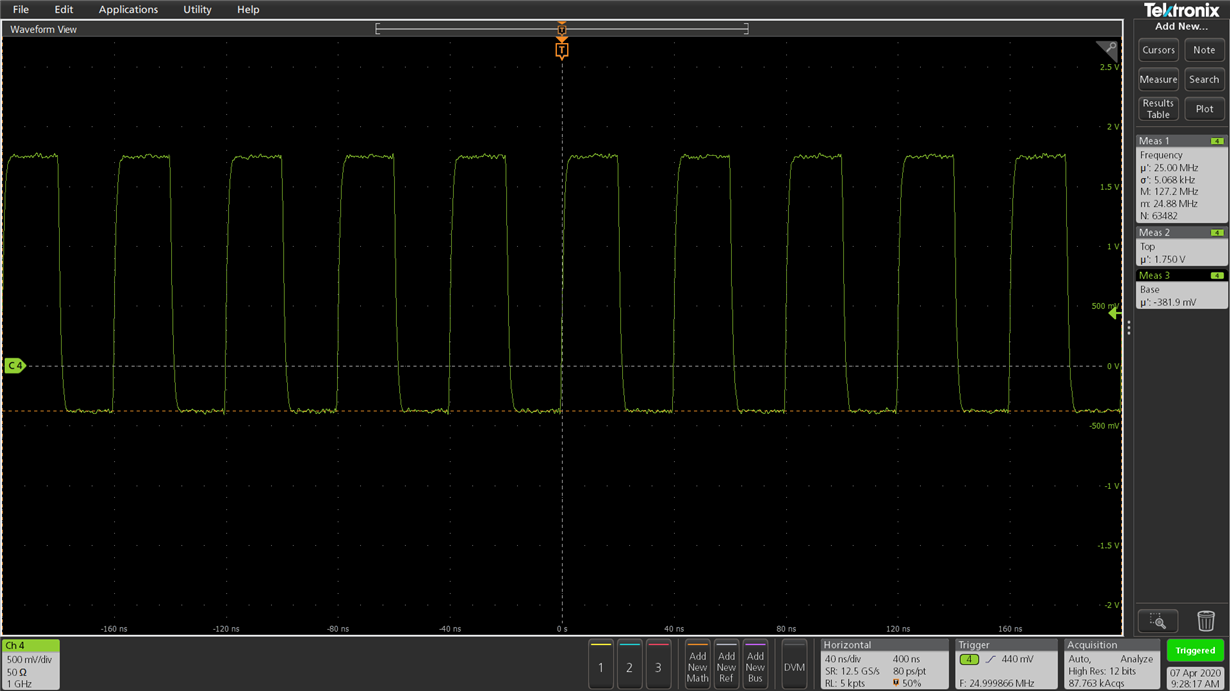

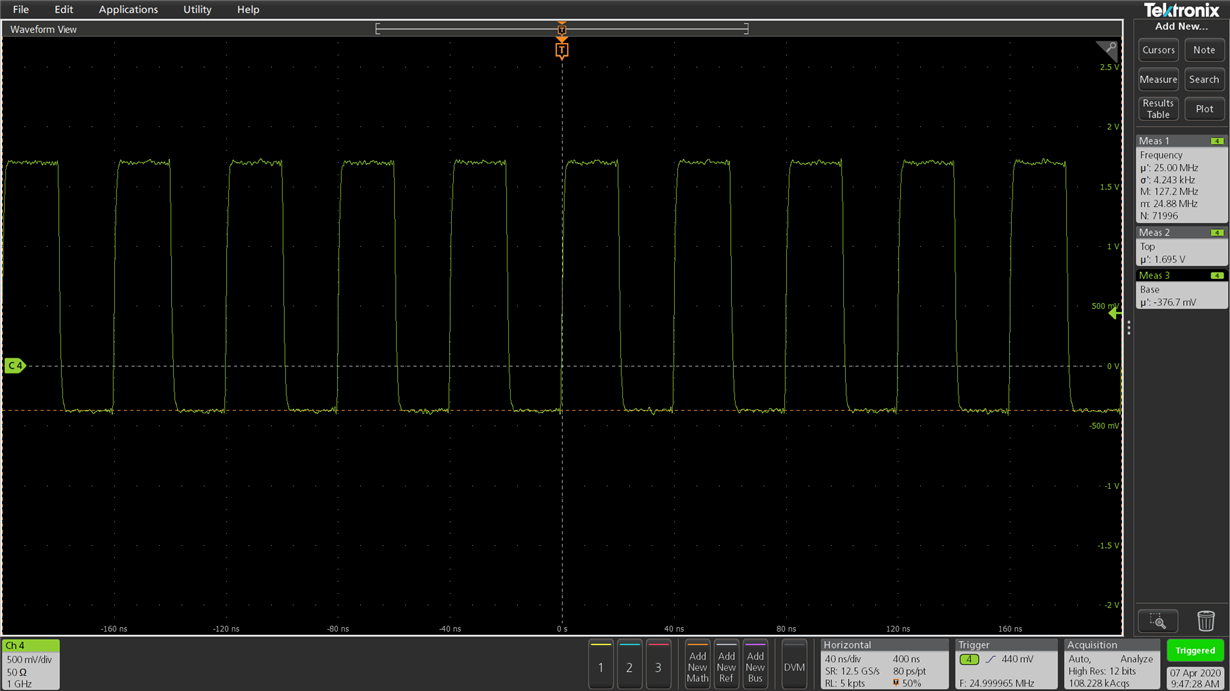

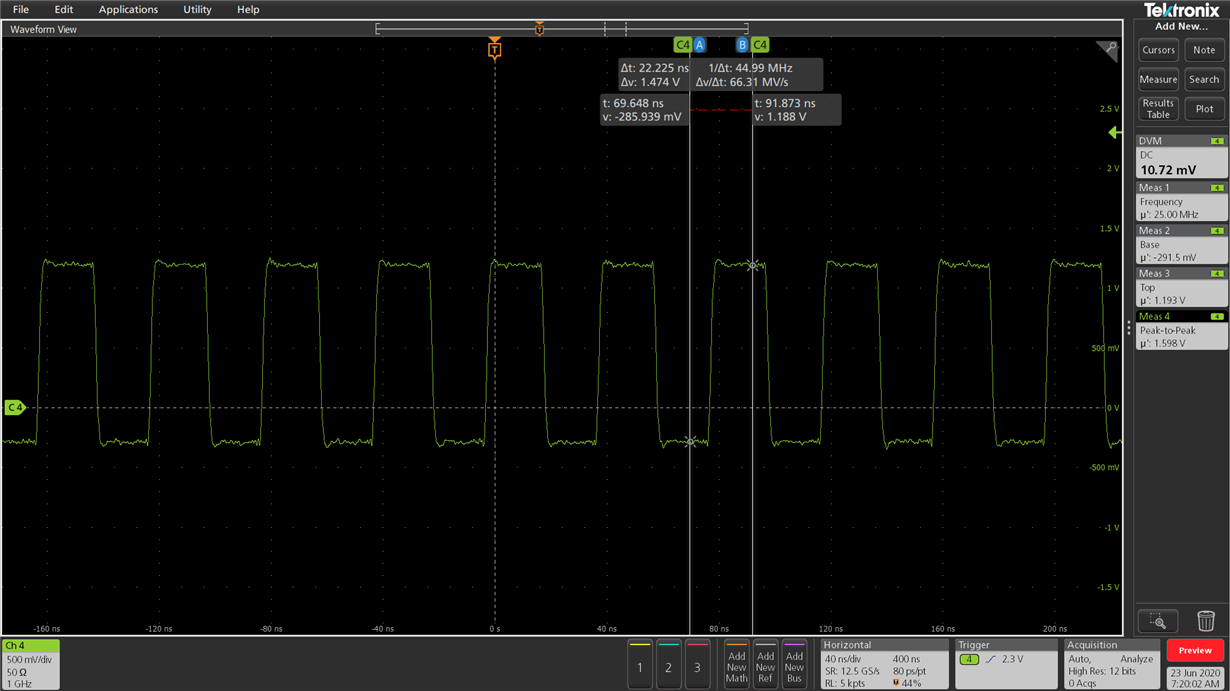

Based on our measurements, AC coupling of signal causes opening of the protective diode of XI pin, and for that reason, base of clock signal is -380mV. It does not meet the requirements from table 7.1 Absolute Maximum Ratings where min. XI voltage is -0.3V.

The reason is clear - because of the use of a capacitive divider, the DC offset of clock signal on XI depends on the internal bias of XI (if any) and on the opening of the protection diode on XI pin. The capacitance ratio CD1/CD2 can only affect the amplitude of the signal, but does not affect the DC offset.

We think that with the use of recommended capacitive divider it is not possible to meet requirements of XI specification and absolute max. ratings.

Can you confirm to us that XI can be long time and stable operated this way (out of the requirements of absolute maximum ratings) or recommend us a better solution?

Thanks and have a nice day

JZ