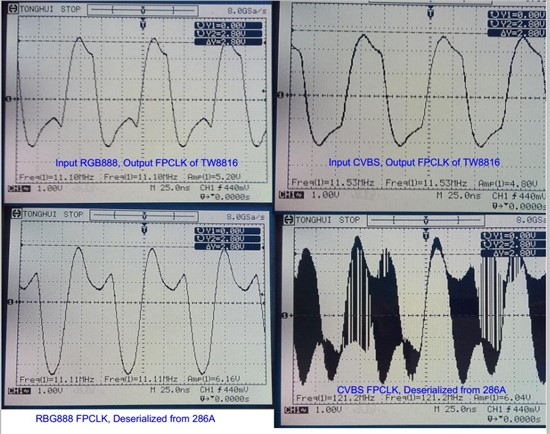

Hi, I have a board with TW8816 as LCD controller and DS90CR285 as transmitter, it's for an old car LCD display and works fine whatever the input of TW8816 is RGB888 or CVBS.

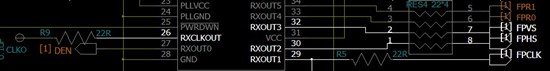

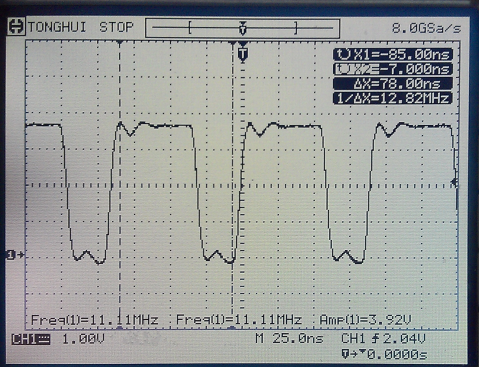

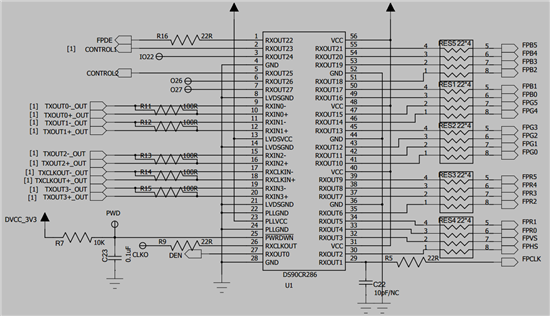

Recently, i made a deserializer board using DS90CR286A,and these two board were connected using board-to-board connector. When the input to TW8816 is RGB888,the singal deserialed good,but when the input is CVBS,then the deserialed signal is very bad. In both case, I measured the FPCLK singal at pin RXOUT1 which was deserialed from RXIN0+/- pair.The frequency of FPCLK in both cases were almost the same about 11MHz.

And the RXCLKOUT was good in both case. Because the original board can light the car LCD dislay all right, i have no reason to be suspicious about it. I can't fingure out why there is such difference in these two cases? Any advice or how should i to find out where may problem be?

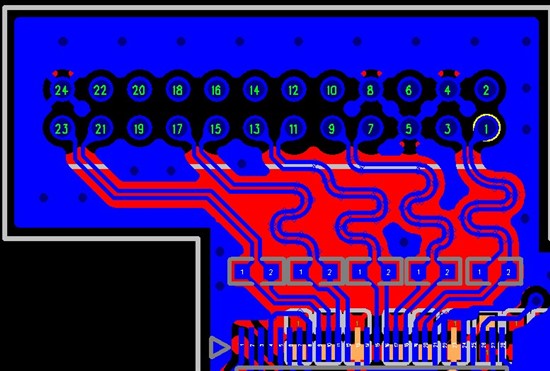

Blow is the screeshot of the FPCLK wave and the LVDS signal PCB layout.