[ DS90UB925 & UB928 ] I2C and AEQ

UB925 and UB928 have “I2C SDA Hold” register to configure the amount of internal hold time.

UB295: 0x17[5:4], I2C Control

UB928: 0x05[6:4], I2C Control 1

Can you help me to understand how this register affect to the timing of I2C communication?

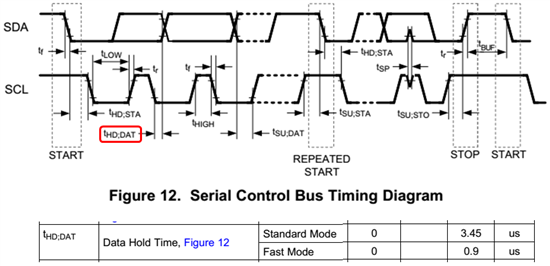

As my understanding, this relates to “tHD,DAT”. Because of I2C specification, there would be possibility that SDA to start transition at the same time with SCL transition.

(tHD,DAT = 0).

For this case, I2C SDA Hold register gives some of delay for SDA, means SDA to be hold internally up to 120nS.

Correct?

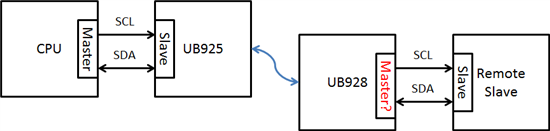

On top of that, does this register only work for slave?

It’s not clear how this register contribute for UB928 as blow which acts like “Master”.

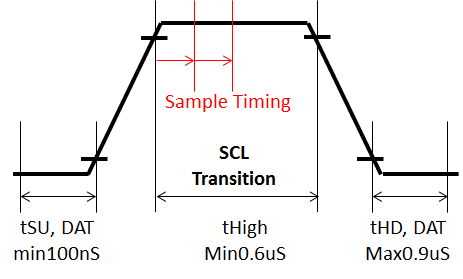

<SDA Output Delay on UB925 and UB928>:

As similar as above, both devices have “SDA Output Delay” register.

Can you please let me know how this work? Which timing are adjusted?

UB295: 0x05[4:3], I2C Control

UB928: 0x06[4:3], I2C Control 2

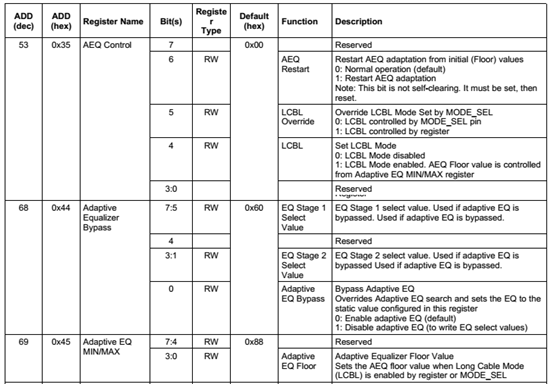

<UB928, AEQ Settings>:

There are some AEQ related control registers on UB928.

When customer attempts to program initial settings, is there any sequence requirement?

As current ideas, customer does not use LCBL, thus “LCBL Override” also left as default.

Drawings in this post can be found in attached pptx.