Part Number: DS90UB948-Q1

Other Parts Discussed in Thread: DRA745

Dears:

Our design meet some issues about DS90UB948 and DS90UB947.

Firstly, is there Errata about DS90UB948 and DS90UB947?

Secondly, during the PP testing in Cars the Infotainment will happen snow dot in screen or screen will change black.

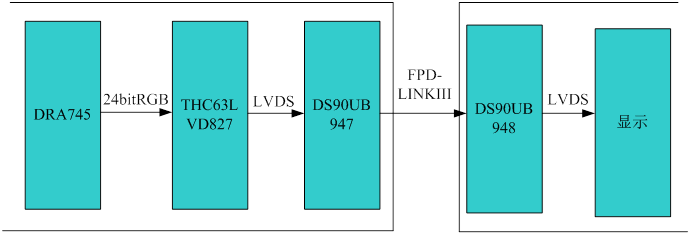

The design's org as below picture(DRA745 sends PCLK is 148.5MHz and RG888 signal for the requirement of 1080p@60HZ):

The specific issues as follows:

- The first issue is screen has back light, however, screen has no image. And the LOCK pin of DS90UB948 is always low level.

So we set off PCLK of DRA745 and set on PCLK again, there is no image. Then software reset DS90UB948 and DS90UB947, there is no image either.

2. The second issue is screen has back light, however, screen has no image. And the LOCK pin of DS90UB948 is always high level.

So we set off PCLK of DRA745 and set on PCLK again, image is OK.

3. The third issue is screen has image, but it will happen snow dots and vertical stripe lines.

Other information as below:

- PDB signal of DS90UB947 is controlled by DRA745;

- We compared the DS90UB947 LVDS CLK’s jitter and eye diagram between the bad board and good board as the below pictures.

a) Good board's eye diagram:

b) Good board's clk jitter:

c)No image board's eye diagram:

d) No image board's clk jitter:

e)No image board's clk jitter:

Btw, there is other question about clk jitter:

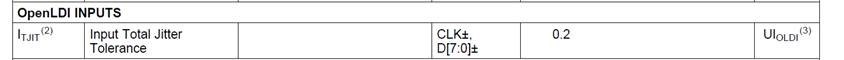

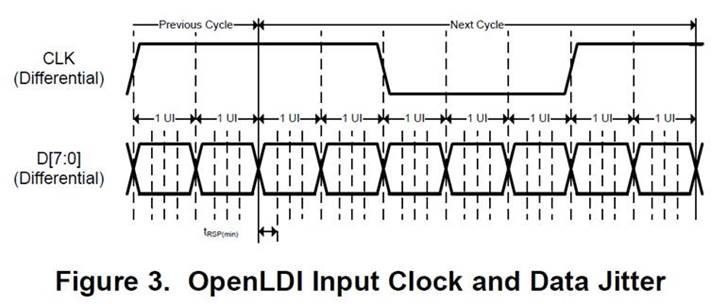

From datasheet of DS90UB947 OpenLDI Inputs as below pictures. The time of 0.2UI is 348.8ps and we want to know the paramate of Input Total Jitter Tolerance whether is only LVDS CLK's jitter or the jitter between CLK and Datas?

(2) Includes data to clock skew, pulse position variation.

(3) One bit period of the OpenLDI input.

Pls. kindly help to give some advice.

Many thanks!

Best regards

Luck Wu