Part Number: ISO1412

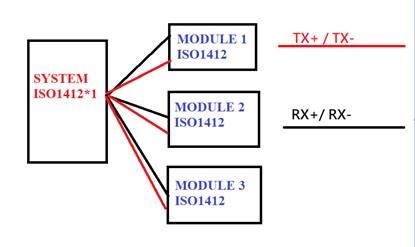

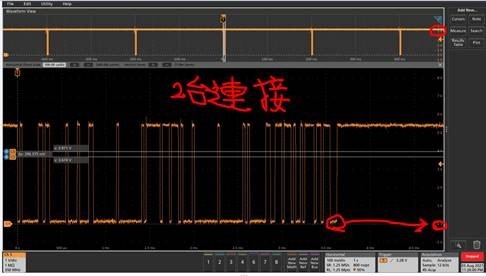

The test we used is shown in the figure below. In the test, only SYSTEM to MODULE 1 is connected, and the measurement graph is normal, but when the SYSTEM is connected to MODULE 1 + MODULE 2, and the RX+ /RX- looks very strange (red mark). May I know is this correct? And what caused this problem.

BR, Gary