Hi,

In our design using ISOW7842, we are facing exactly the same behaviour of the "VISO latch-up" as described in this thread: https://e2e.ti.com/support/isolation-group/isolation/f/isolation-forum/769224/isow7842-latch-up

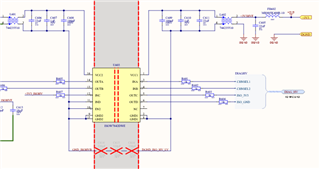

Please find below the schematic. We are using this circuit 3x in parallel, supplied by one TI PMIC TPS65381.

VCC = 3V3 and VISO = 3V3

At startup sometimes VISO goes to >6V, a noise frequency is clearly audible and the component starts heating. It happens 90% on the same component, but it can happen rarely on another of the 3 we have in parallel.

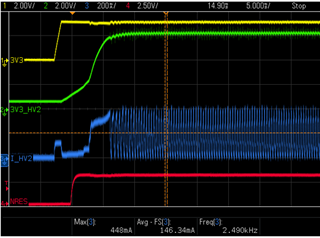

Please find below a print screen of a bad starti with

- 3V3 VCC in yellow

- 3V3 VISO in green

- Current on 3V3 VCC input in Blue

The load on ISO side is about 25mA.

The recommendation that can be found in this forum and in previous datasheets is to add a bigger capacitance on VCC side of around 100uF. We can see that along the years that this recommendation has been removed from datasheet revision F. Could you explain why?

Do you have any idea of what are the causes of this problem?

Thx,

Pierrick