Other Parts Discussed in Thread: SN6505B

Tool/software:

Dear Sir,

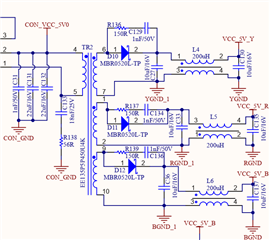

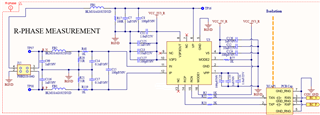

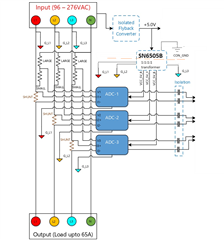

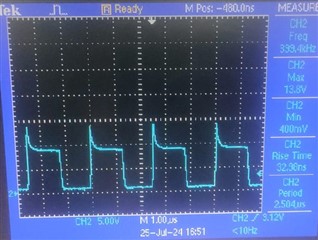

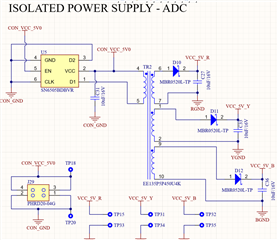

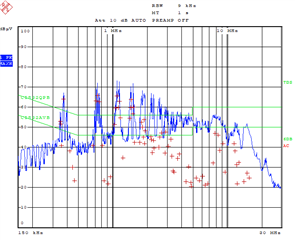

SN6505BDBVR is used in our design in flyback mode to generate the 3 power supplies for the ADC of the 3-phase smart meter. During the conducted Emission test as per the CISPR 32: 2015 standard, it fails at multiple frequencies as shown in the below image. We have also tried several combinations of the snubber circuit on the primary and secondary sides of the transformer according to https://www.ti.com/lit/pdf/SLLA566 but we are still unable to improve the results. Please provide your valuable input to resolve the same as soon as possible. Let me know if you need more information.

Regards,

Nilesh