Part Number: ISO6720

Other Parts Discussed in Thread: LMX1214, LMX2582, ISO6741, ISO7741

Tool/software:

Hi,

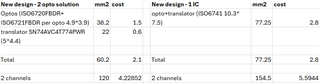

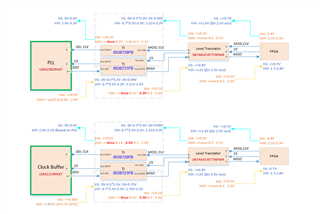

Our legacy design has SPI interface between FPGA and PLL. It uses HCPL-063L-000E (to isolate SDI,CLK,CS to PLL) and ACPL-077L-000E (to isolate SDO from PLL). With change in PLL to LMX2582 and clock buffer to LMX1214, to meet the voltage loading requirement, I am considering changing the optos.

1. Is ISO6720FB and ISO6721FB combination a good alternative? else pls recommend suitable alternative. product is an industrial scanner and SPI runs at ~15MHz

2. I plan to use 2 forward channels of ISO6720FB for SDI, CLK. And ISO6721FB for CS forward channel and SDO reverse channel. Or would you recommend a different combination?

3. Can you please check the below snapshot to see if this will work?

(Note: FPGA SPIs are 2.5 LVCMOS, level translator will have to convert 2.5V from FPGA to 3.3V, PLL SPI voltage is 3.3V, CLK buffer SPI is 2.5V)

Thanks