Other Parts Discussed in Thread: SN6507

Tool/software:

Hello TI,

we are facing issue with SN6507 push-pull transformer driver which is in our power converter supplying IGBT gate driver via transformer - please see attached schematic .

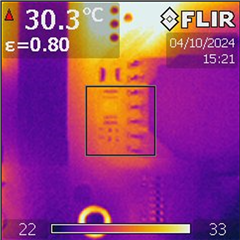

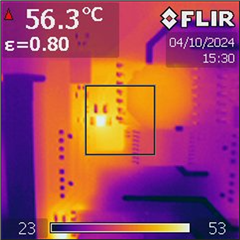

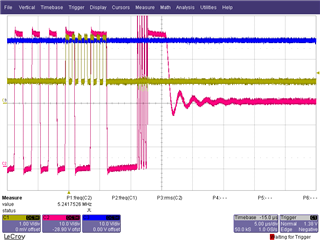

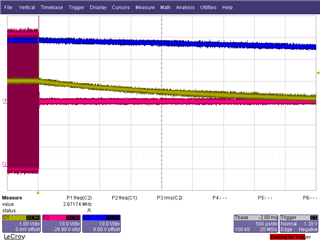

Multiple of SN6507 are operating normally (usually) in our system. With certain pulse pattern in high power electronics circuit, we are facing latching behavior of SN6507, which is not explainable by the datasheet. Latched mode is permanent, practically up to next power cycle of the input voltage. After cycling the input power, SN6507 continues operating normally, no degradation of performance. During the latched condition, steady voltage on SW1&SW2 (no switching). IC goes to complete idle condition, input voltage is 29,8V.

By comparing the voltages on pins before and after the event causing the latched mode, we see that CLK voltage drops to 0V. At normal operation, it is typically around 0,98V. Voltages on other pins in latched condition, seem to make sense - PIN4 FB 6.8V (29.8Vin), PIN6 SR 1.132V.

There might be a short glitch, voltage induced in CLK pin loop, from power electronics circuit which might result in voltage on CLK pin above 1.6V, but this shall not create a permanent latch of the IC, at least not according to the datasheet.

Can you please suggest what might be the root cause of this behavior and how to avoid it? Is the filter capacitor (e.g. 100nF) on CLK signal acceptable (no influence in normal operation)?

Thank you very much,

Best Regards,

Michal