Tool/software:

Hello,

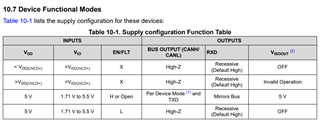

I am wondering if it is safe to have VIO powered with 3.3V and Vdd not powered (0V) for this IC for when not in use. Vdd is powered off 5V when in use, but we want to disable the 5V regulator to conserve power. The 3.3V regulator will remain on at all times.

Thanks,

Gabe