Tool/software:

Hello,

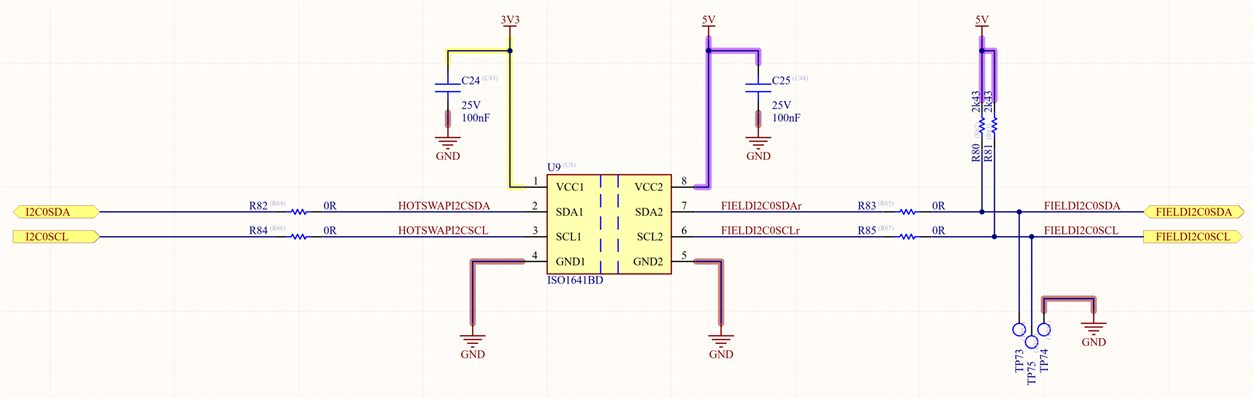

We are using the ISO1641 in an I2C level translation application with Side 1 at 3.3 V and side 2 at 5V. We do not need the isolation feature, so the grounds on both sides of the device are tied to our common ground net. We have SDA and SCL pull ups on both sides of the device at 2.43 kOhms each. We are observing that in a 6 byte transaction across the level translator, that occasionally clock pulses on side 1 are not being mirrored on side 2, instead side 2 is just held low for the clock pulse. We're not going fast, this is at 100 kHz. When the clock signals are passing through, they look quite clean on the oscilloscope on both sides of the isolator/level translator. On the primary side, we have 2 other I2C devices connected to the bus (3 if you include the master). I wouldn't expect this to violate the capacitance limitations, and if it did I'm surprised that we'd so consistently have the same clock pulses not getting through. I'm wondering if you have any recommendations for what to try to resolve this issue?

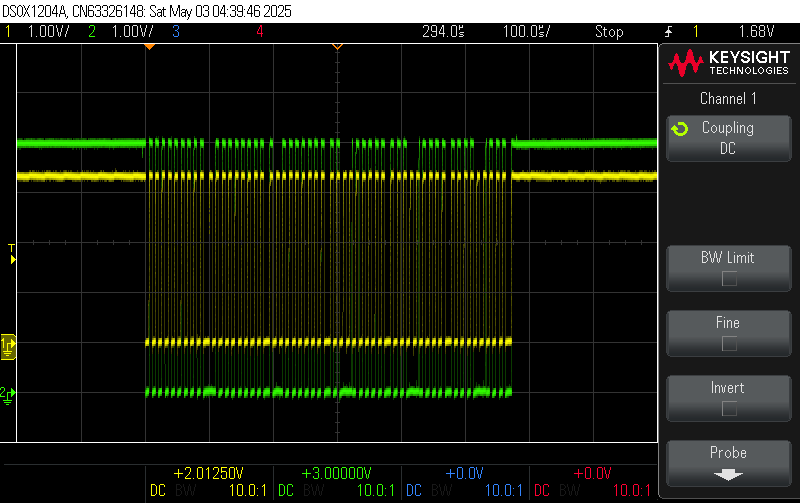

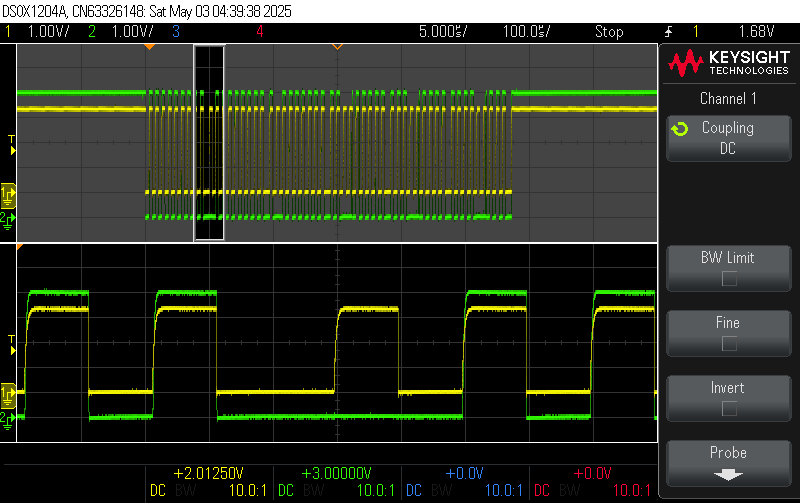

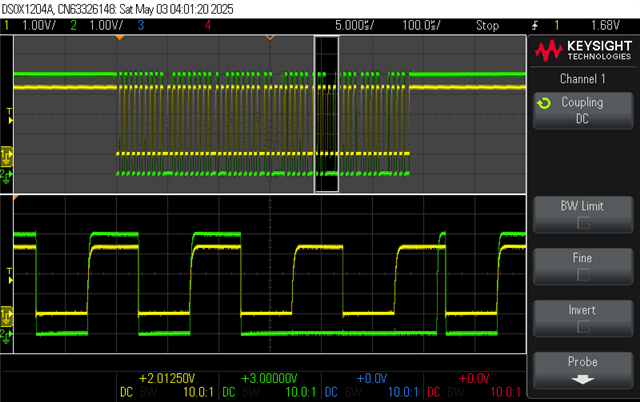

In the scope traces below, the yellow trace is the side one CLK signal at 3.3 V, and the green trace is the 5V secondary side clock. You can see that some of the yellow clock pulses are not making it from side 1 to side 2, and sometimes part way through the primary side clock signal the secondary side suddenly rises up and starts tracking the primary side again.

Thanks,

Neal