Other Parts Discussed in Thread: ISO1540

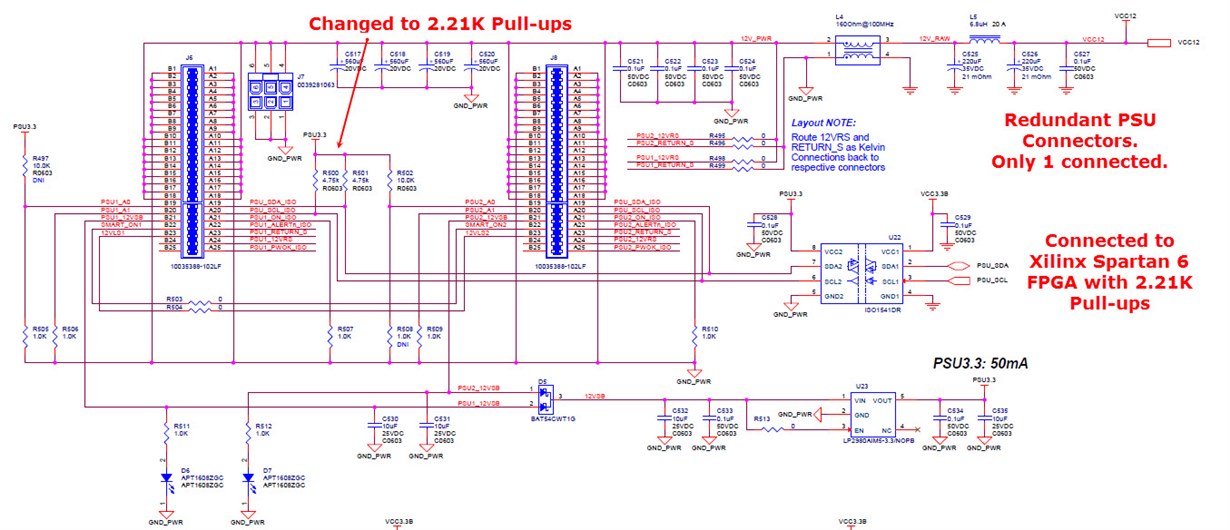

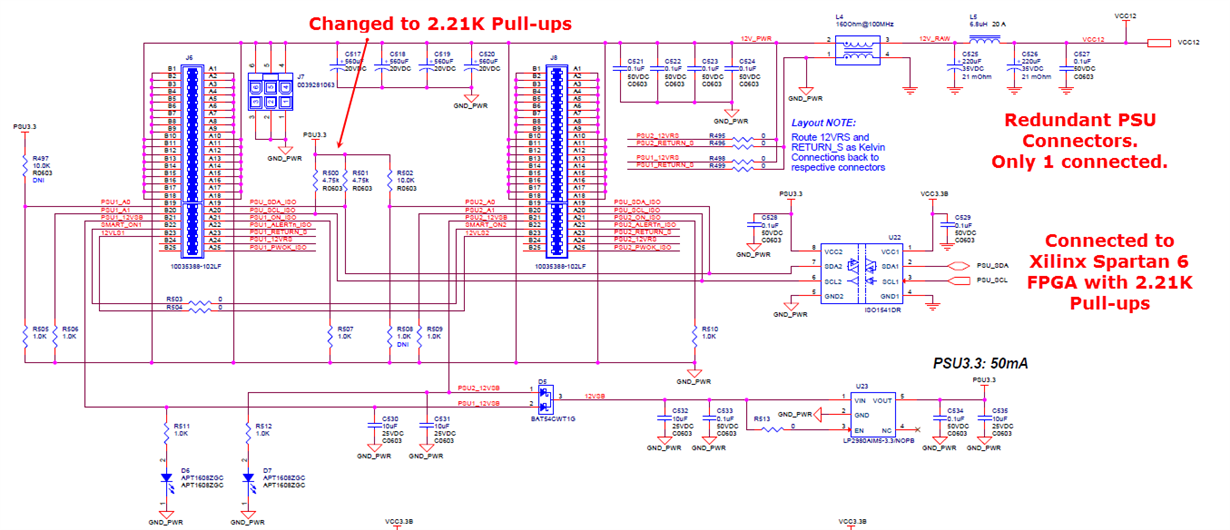

Having Issues with the Slave side clock disappearing at the output side (Side 2) of our ISO1541. Master is a Xilinx FPGA connected to Side 1 of the ISO1541, Slave is a Delta Power Supply. We are trying to perform PMBus operations and are unfamiliar with PMBus though it seems I2C/SMBus are the PHY layer of the comm link.

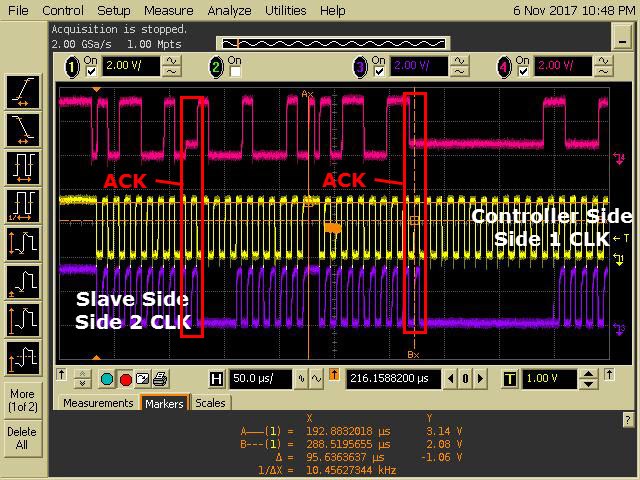

It seems that the Clock disappears from the output of the ISO1541 after the slave ACKs a transaction. Below is a scopeshot of the Controller side SDA, SCL and the Slave side SCL.

Could this be the slave stretching the clock? I've never come across clock stretching so am unfamiliar with it.

Thanks for the help

-Jack