Hi ti team,

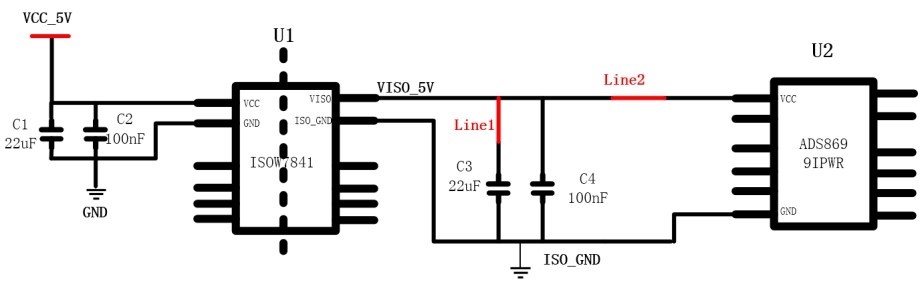

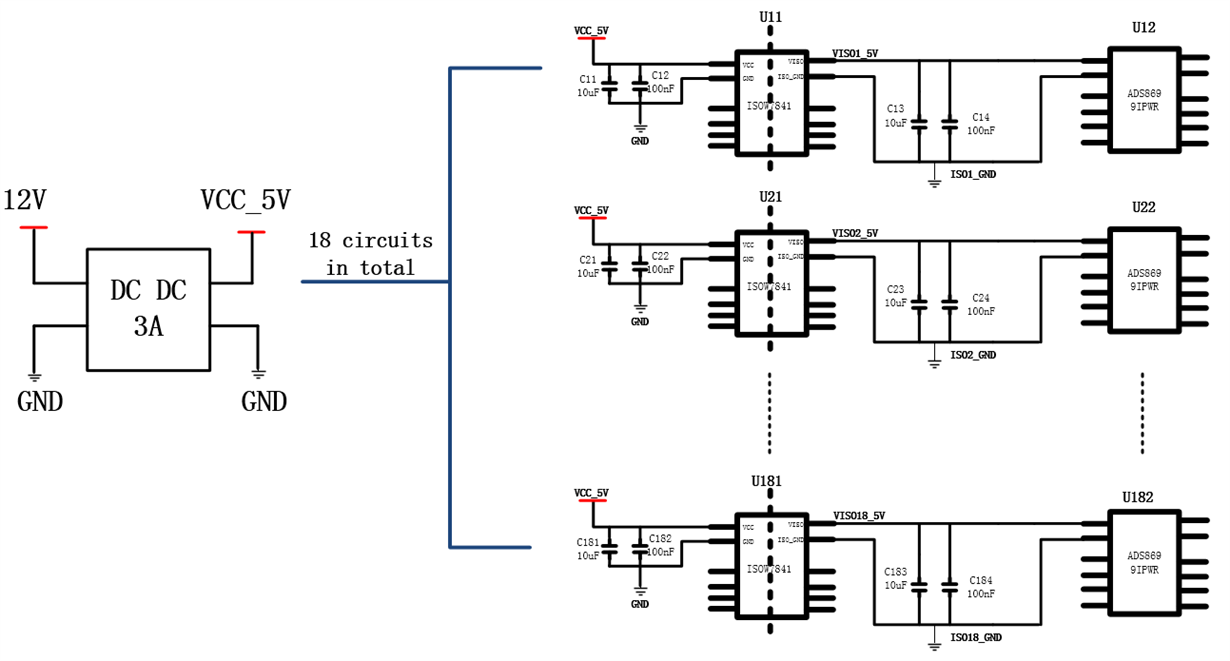

At present, an isolation chip of TI "ISOW7841DWER" and "ADS8699IPWR" chip are used to complete the isolation voltage collection function. The specific hardware circuit diagram is as follows.5V power supply is provided. During the debugging process, it is always easy to have a short circuit at the 5V power pin of the isolation chip "ISOW7841DWER" near the chip side of "ADS8699IPWR", resulting in abnormal heat of the isolation chip and damage of the chip.

According to the previous situation, made an adjustment to the circuit, the back-end "ISOW7841DWER" chip capacitor C3 values by 22 uf replacement for 10 uf, "ISOW7841DWER" chip damage problems exist no longer, but using current clamp test, Line1 location, observation by capacitor C3 current waveform that, in the electric moment, through the C3 of around 130 ma peak current, and the chip datasheet above show that chip can withstand 130 ma,

please help to analyze,Is the chip damaged because the isolated output current is too large?

which leads to the damage of the internal rectifying current of the chip, short-circuit the output power supply, and is the value of the bearing current on the datasheet available for reference at design ?

Thank you very much!