Other Parts Discussed in Thread: ISOW7841,

Hello,

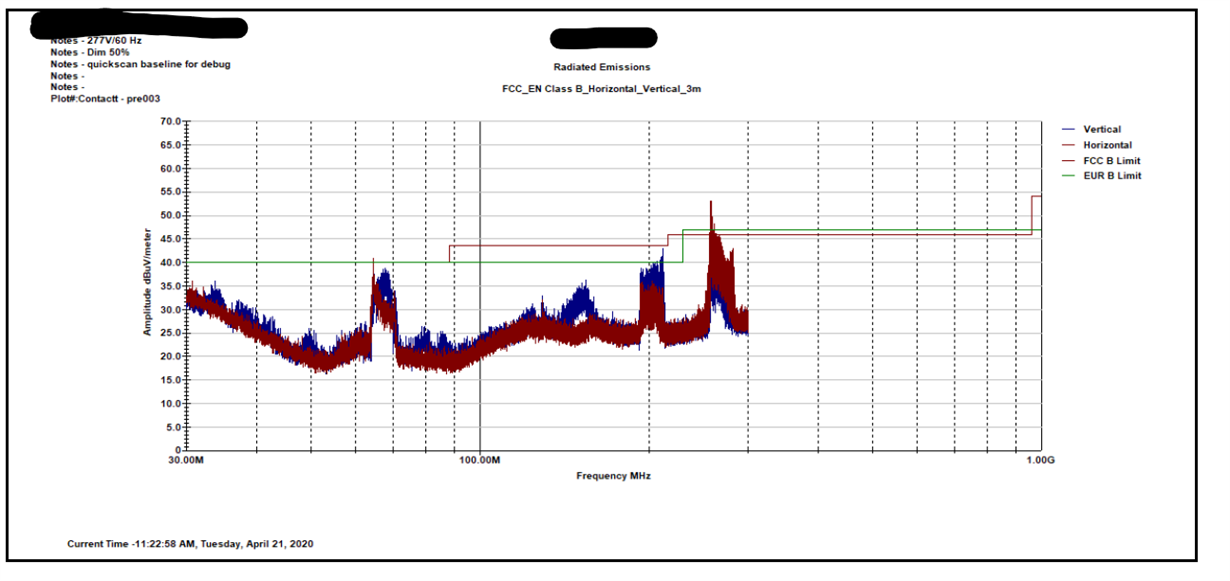

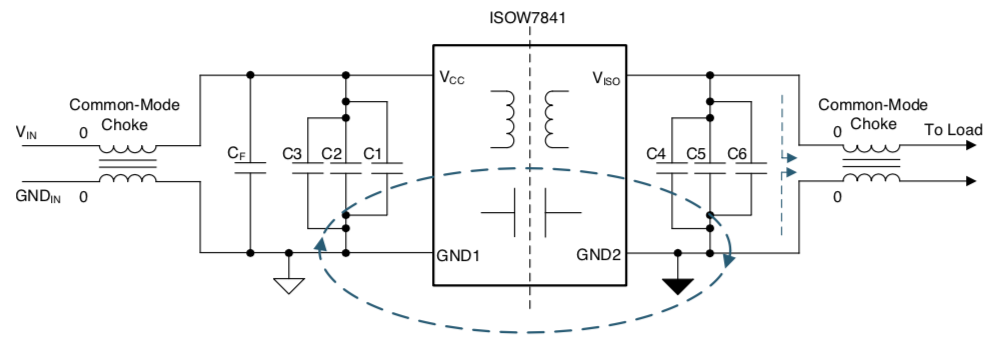

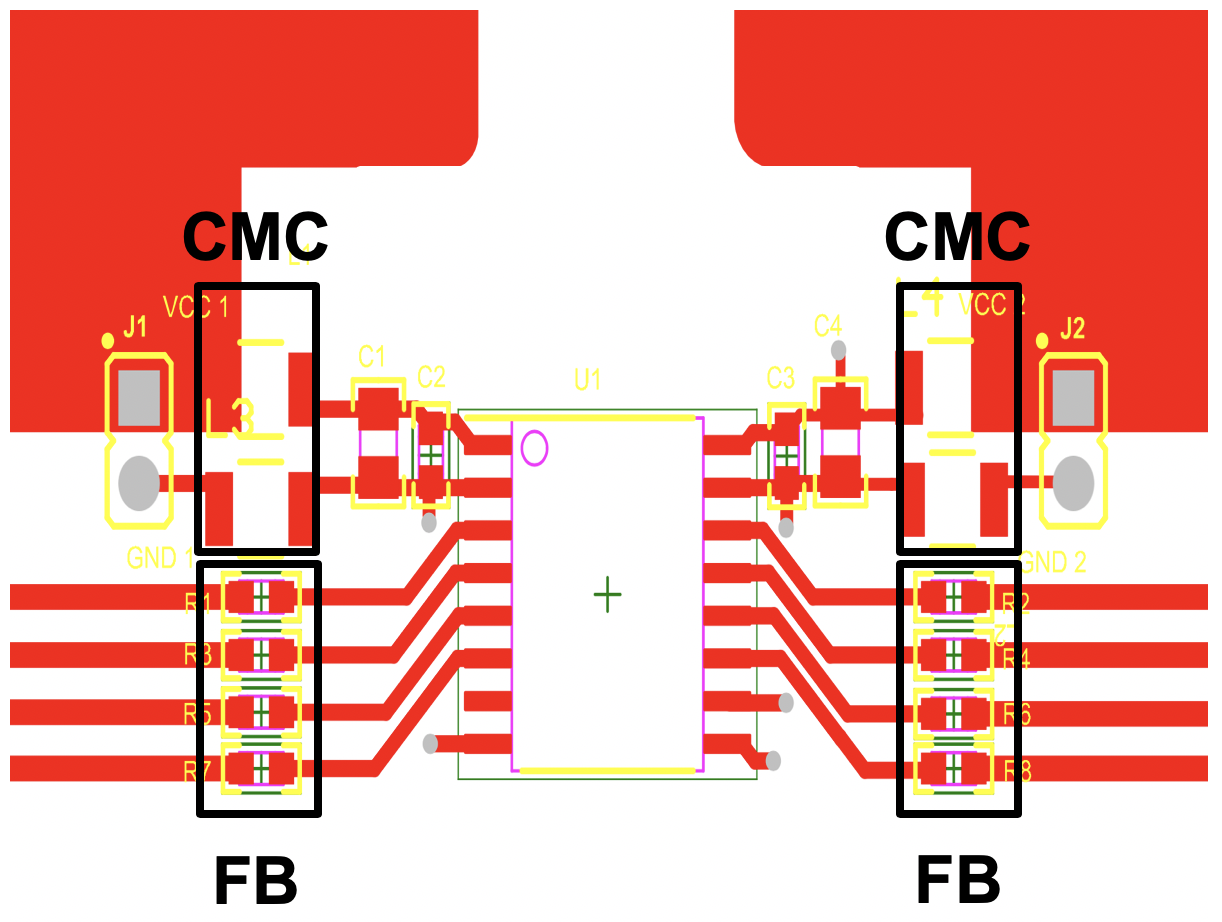

I have a design using the ISOW7842. I followed the guidance in SLLA368C "Low-Emission Designs With ISOW7841 Integrated Signal and Power Isolator" However the design is failing FCC Class B

I was able to add an inter-plane capacitance of about 20pF. This is the 2nd scan of the device and was a quick scan from 30-300Mhz.

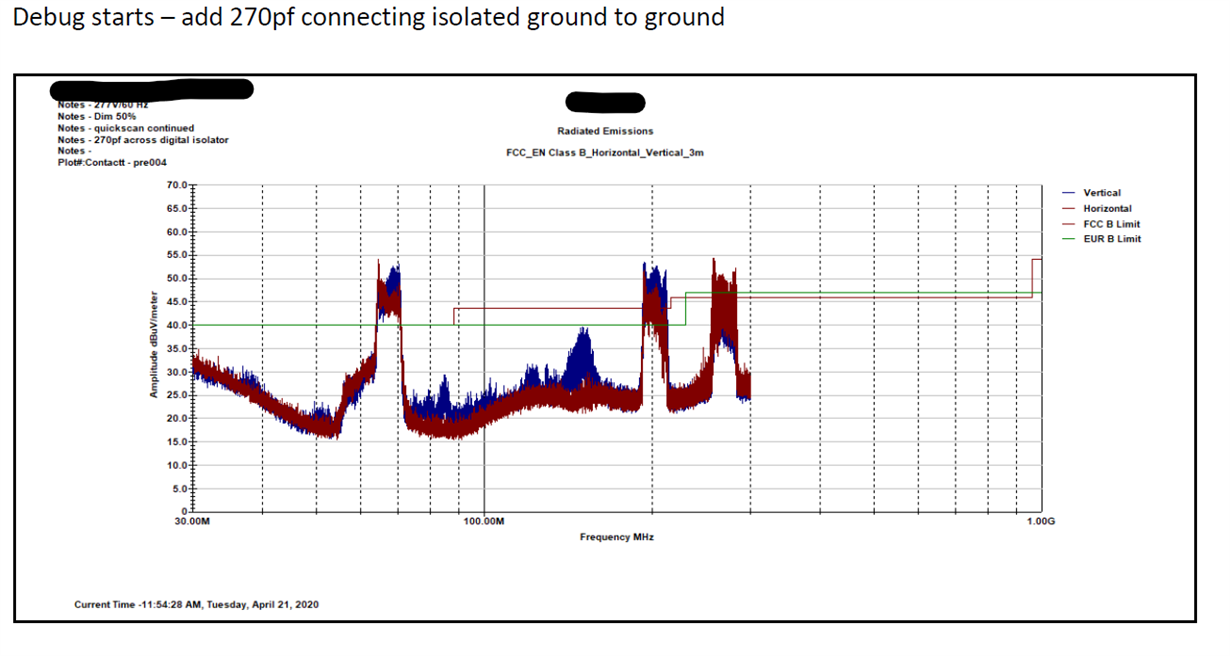

Here is the 3rd scan with a 270pF capacitor soldered across the grounds of the isolator. As you can see...this only made things much worse.

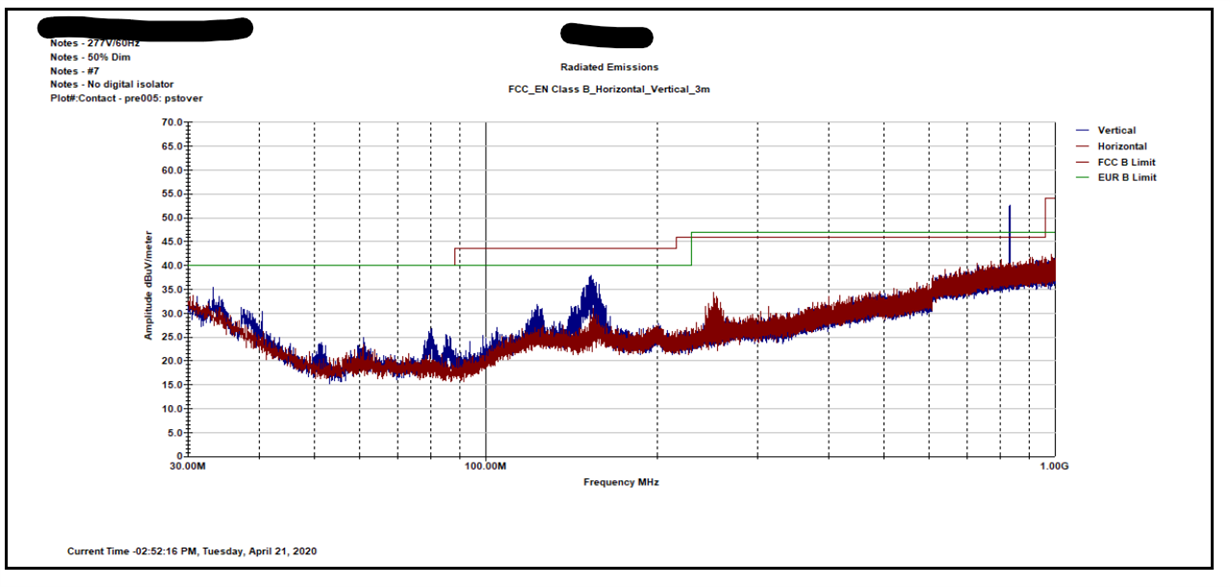

Here is the scan without the isolator IC removed from the board.

Please let me know your thoughts on this. I would able to share more information in a non-public forum.