Hi,

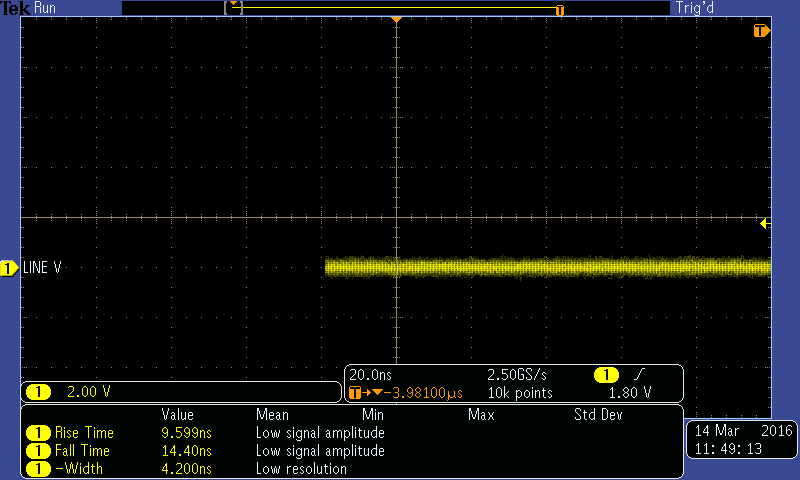

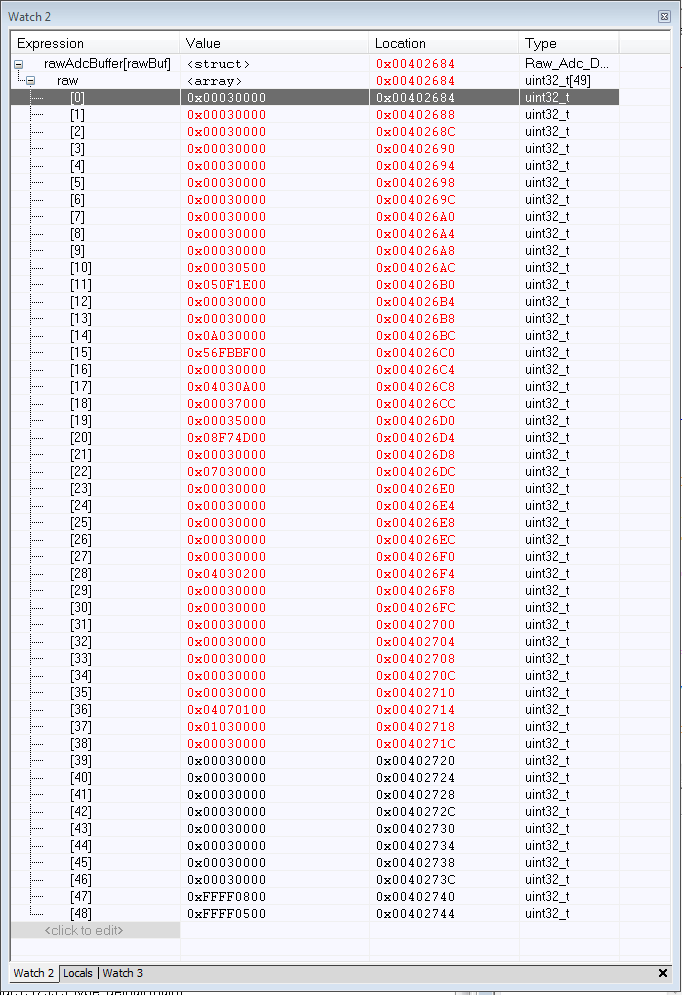

I have a SPI-DMA setup on TMS470R1B1M to fetch data from ADC (ADS1278). This is a 24bit ADC and there are 8 channels. So we read 24 bytes on every ADC cycle. It reads good data but once in a while on power up it starts reading bad values. I have a constant voltage fed to ADC channels. When it reads the bad values, the values jump all over the place. After some debugging I realized that the first byte is some bad value but then the rest of the data corresponds to the good data bytes, but now everything is offset by 1 byte in the array due to the first bad data byte. Also the last byte is lost. I verified that the ADC is sending good values as I gather them on scope. I see that it is sending good packets over SPI. My conclusion is that the DMA is the culprit which somehow does not increment the destination address properly.

Any idea what could be going wrong. I tried to halt the DMA (which should reset the internal regs, but this did not help.

My DMA setup is as follows:

******************* DMA Setup ******************************

// DMA setup for SPI1:RX (Packet 1/Channel 1)

// Control Packet 1 Configuration

DMAC01 = 0 | TRSIZE_0 | INTEN | DSTINC | DSTMOD_2 | SRCMOD_15;

DMASA01 = (uint32_t)&SPI1BUF + 3; // Interested in the Lowest Byte so skip first 3 bytes (SPIBUF is 4 bytes)

DMADA01 = (uint32_t)rxbuf;

DMATC01 = 24;

// Notify the DMA that Control Packet 1 is updated

DMACPS |= CPACK_1;

// Channel 1 Configuration

DMACC0 |= SEN1 | RQEN1;

// Channel 1 Enable with Control Packet 1

DMACCP0 |= CCPACK1_1 | DMEN1;

// DMA setup for SPI1:TX (Packet 2/Channel 2)

// Control Packet 2 Configuration

DMAC02 = 0 | SRCINC | SRCMOD_2 | DSTMOD_15;

DMASA02 = (uint32_t)txbuf;

DMADA02 = (uint32_t)&SPI1DAT0 + 3; // 1;

DMATC02 = 24;

// Notify the DMA that Control Packet 2 is updated

DMACPS |= CPACK_2;

// Channel 2 Configuration

DMACC0 |= SEN2 | RQEN2;

// Channel 2 Enable with Control Packet 2

DMACCP0 |= CCPACK2_2 | DMEN2;

****************************************************************

byte rxbuf[24], txbuf[24];

************** SPI-1 Init *****************************************

// Enter SPI reset mode

SPI1CTRL2 &= ~SPIEN; // Place SPI in reset

SPI1CTRL3 &= ~RX_INT_EN; // Disable SPI receive interrupts

// Configure SPI port 1

SPI1CTRL1 = 0 | CHARLEN_8; // 8 bits/char

SPI1CTRL1 |= SPI_PRESCALE_47; // ADC Clock = 1 MHZ

SPI1CTRL2 |= MASTER; // We are the master

SPI1CTRL2 |= CLKMOD; // We drive the clock

SPI1CTRL2 &= ~POLARITY;

SPI1CTRL2 |= PHASE;

SPI1PC6 = 0 | CLK_FUN; // SCLK pin

SPI1PC6 |= SIMO_FUN; // SIMO pin

SPI1PC6 |= SOMI_FUN; // SOMI pin

SPI1CTRL3 |= DMA_REQ_EN; // DMA request enable

SPI1CTRL2 |= SPIEN; // Activate the SPI

************ DMA Init *****************************************

DMAGC = 0; // Channel service size = 1

DMAGD = 0; // Clear STOP and HALT mode

DMACPSCLR = 0; // Disable all control packets

DMAS = 0; // Clear all pending interrupts

DMACCP0 = 0; // Disable channels 0-3

DMACCP1 = 0; // Disable channels 4-7

DMACCP2 = 0; // Disable channels 8-11

DMACCP3 = 0; // Disable channels 12-15

************************************************************

I would appreciate some help on this.

Pinakin