Hi,

We have been working on a board for time measurement application for the past two years using your THS788 TMU, and we discovered this week that is was operating in a very weird way when using a higher clock rate for the SYNC input.

Here is the situation :

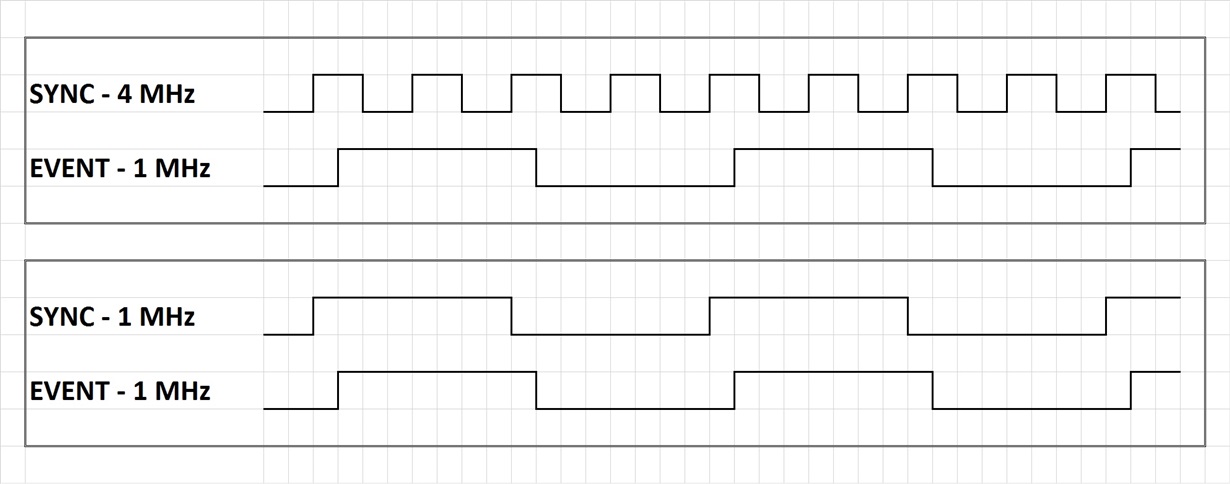

- We are using it in a SYNC-SYNC-SYNC-EVENT processing way, which means many sync period can have no event pulses.

- The chip runs perfectly using a 1MHz SYNC clock and a 1 MHz EVENT input rate using the oboard pulse generator, with a 8ps sigma as promised.

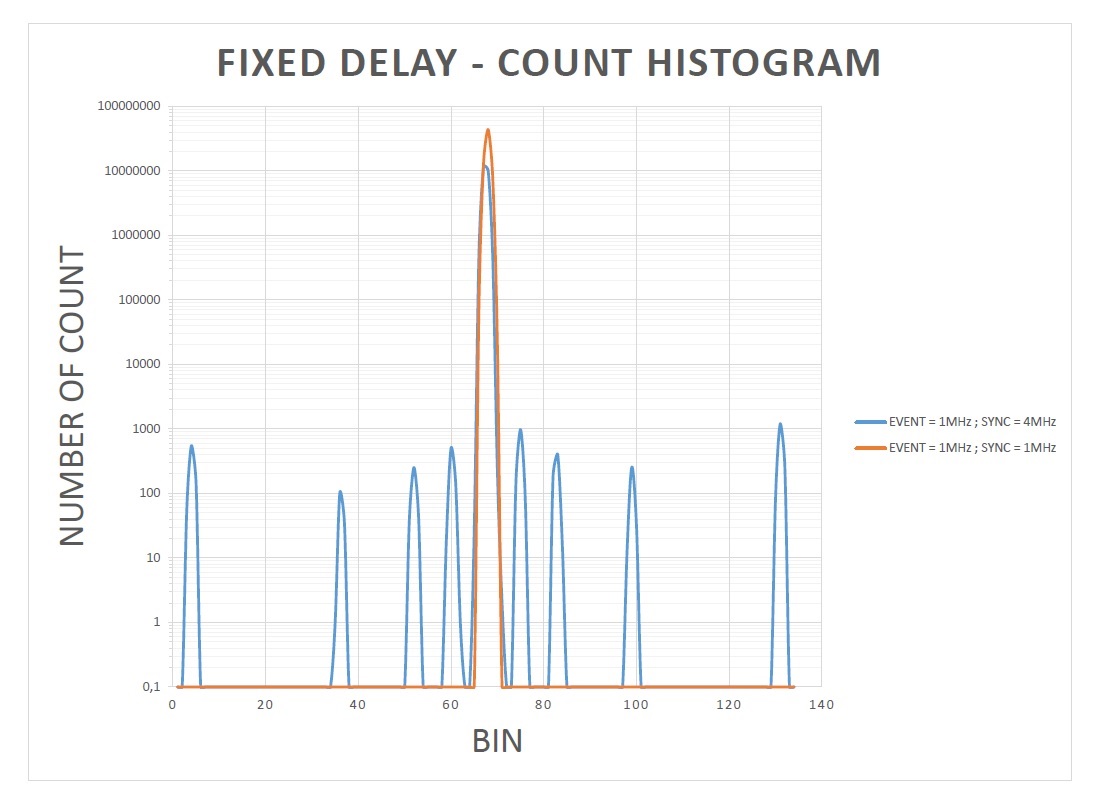

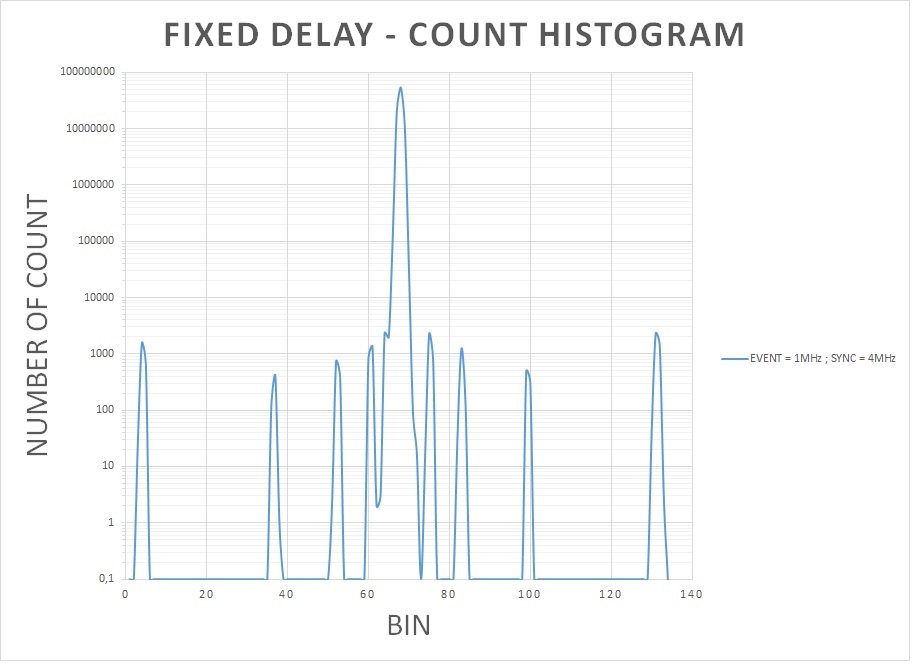

- When using the exact same event input (1 MHz), but a reference clock at 4 MHz, some quantification error start to occur generating really weird histograms. Some smaller peaks appear at (Main peak + 8/16/32 bins). I have attached a picture of this histogram. I have used a logY axis to show more clearly the problem.

I cannot understand why this happens, and it becomes worst as the frequency of the sync pulse increases.

Since this system is supposed to work at a 80MHz SYNC rate, it is impossible to make this project work without understanding what is happening.

Here are some of the operating specs :

-Data clock rate : 150MHz

-Positive to positive Edge

- 34 bit global counter

- 16 bit results output

- No holdoff - No calibration - No arming conditions

- All power supply are low noise LDO

-All signal are buffer with extremely high rise time

-TDC is cooled with heatsink and fan

I understand that this product is now NRND, but I still need to make that project work... We have a lot of money invested in this and we need to find a way to make the THS788 work.

Please advise...

Jonathan