Hi,

I'd like to ask about following things,

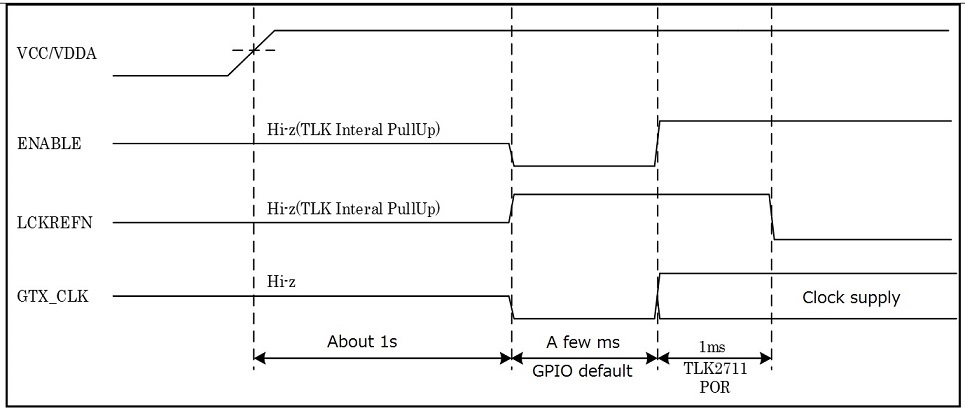

1. When we use TLK2711-SP as transmitter only, we should drive LOOPEN and LCKREFN to LOW after Internal POR completed.

How long should we wait before driving LOOPEN and LCKREFN to LOW for appropriate operation?

Is it OK that wait at least 1ms?

2. Question about the timing between VCC/VDDA and GTX_CLK during POR,

Should we supply GTX_CLK before VCC/VDDA reaches 2.375V?

3. Is there any problem about the attached POR sequence for appropriate operation?

Regards,

Go