Other Parts Discussed in Thread: TMS320F2810, TMS320F28335

Tool/software: Code Composer Studio

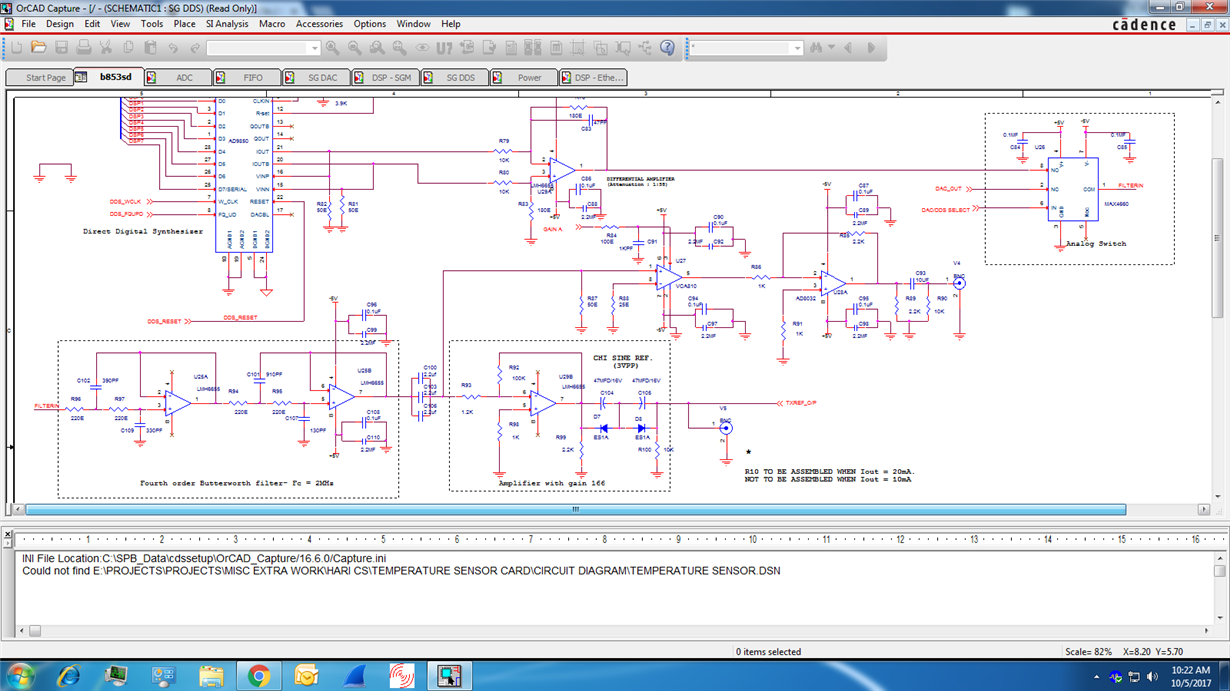

i have generated chirp signal in matlab , there are 1000 samples. now i have to load this signal to fifo and from fifo to dac, i have doubt in loading the signal to fifo. how to code that part?