Hi Team,

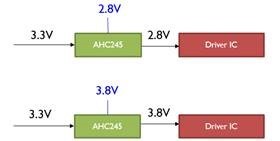

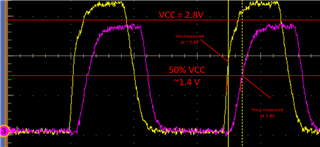

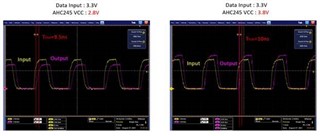

I want to check the tPLH and tPHL parameters in datasheet. I find below table in datasheet. It seems like that the parameters is related to Vcc and Cload on PCB trace.

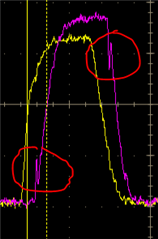

Below is our measurement. We measure the SN74AHC245 pinout directly.(Input & Output) The delay time is around the 10ns. It can meet the max value showing in datasheet, but we measure the pinout directly. Does it mean that our Cload is much smaller than 15pF?

And below is my questions.

1. From our test result, is it make sense to you

2. How could we define Cload? Equivalent cap on PCB trace? If we measure the pinout directly, can we say Cload = 0?

Roy