Hello,

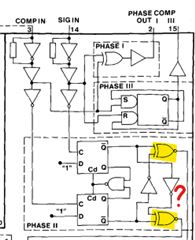

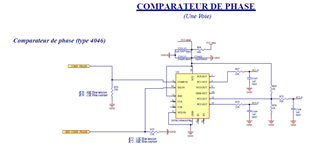

when I compare PC2 Average Output voltage vs Input Phase Difference Characteristic, I obtain with my mockup, to the one in the datasheet,

I have a negative slope instead of a positive slope (while PC1 and PC3 have a positive slope like in the datasheet, so it's not an inversion of the 2 inputs).

Could you explain me why ?

Thank you