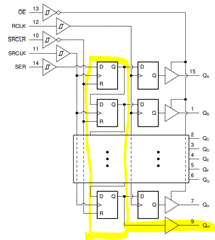

I am planning on chaining multiple shift registers together to get more states.The data sheet for the P/N #54HC595, (8 bit shift register) has an Qh output and a QH' output. The Qh' output is about a half clock cycle behind the QH signal. To chain two of the 54HC595 shift registers together, I believe I should be sending the Qh signal into the "SER" pin of the following shift register. Can you please let me know if my understanding of combining two 54HC595 shift registers is correct. Thanks Bob Wagner.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.