Other Parts Discussed in Thread: TMP144, , TXU0204

Hello,

I am working on an application where I plan to interface a TMP144 temperature sensor (which operates at 3.3V logic levels & 5kbps baud rate) with a 5V UART logic field bus. I intend to use the SN74LVC07A hex buffer with with 3.3V Vcc & open-drain outputs for level shifting. Power consumption is not a constraint. Here are the key details of the configuration:

- Level Shifting from 5V to 3.3V: For the UART Tx line from the 5V field bus to the sensor

- Level Shifting from 3.3V to 5V: For the UART Rx line from the sensor to the 5V field bus

- Clock Signal Translation: Additionally, using seprate buffer - translating a 4MHz clock signal from 5V to 3.3V logic level for an MCU

The SN74LVC07A is powered at 3.3V, and according to the datasheet, it supports input voltages up to 5.5V, making it suitable for interfacing with the 5V logic levels of the field bus. The datasheet also mentions that both input & output are 5.5V tolerant & the device can be used to translate upto 5.5V or down to VCC.

I have a couple of questions regarding this setup:

- Is this configuration appropriate for the bidirectional UART communication using two seperate channels as required for interfacing the TMP144 sensor with the 5V bus while the buffer is powered by 3.3V VCC?

- Can we continue with the assumption based on datasheet that the outputs can be safely pulled up to a voltage higher than VCC ie 5V when powere by 3.3V VCC

- Are there any additional considerations or potential issues I should be aware of, especially regarding the reliability of the level shifting for the UART communication lines?

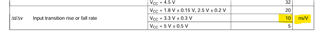

- Is the idea to use one of the channels for level translating 5V & 4Mhz logic signal into 3.3V signal that can be fed to Clock input of MCU? We will take care of the rise time & the fall times by suitable R-Pull up.

Any insights or recommendations for this type of application would be greatly appreciated.

Thank you!