Other Parts Discussed in Thread: TXB0106

Tool/software:

Dear Team,

Greetings from Dialtronics Systems Pvt Ltd., INDIA.

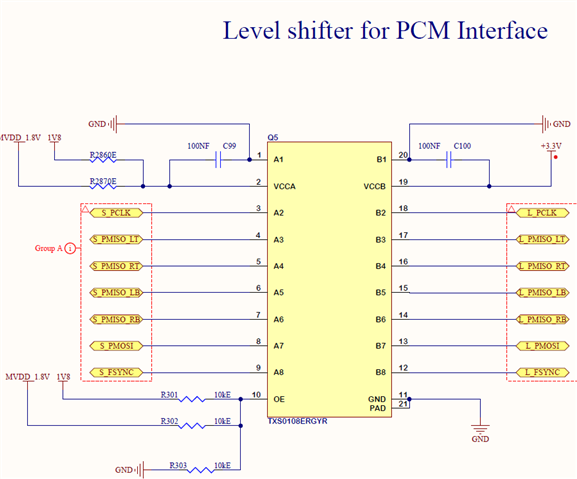

We are using TXS0108ERGYR voltage level shifter from Texas Instruments.

In the above schematic, we are populating R286, C99, C100.

Case1: Tried making OE as pull down through 10KE.

Case2: Tried making OE as pull up through 10KE.

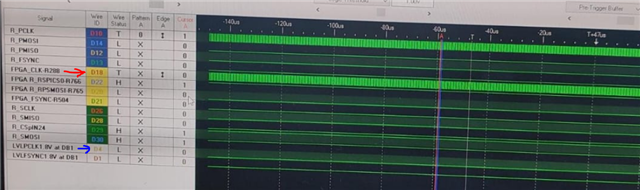

In both of the cases we are not getting expected output from the level shifter.

Our Requirement: Input to the level shifter is 3.3V PCM Signals

Expected output from the level shifter is 1.8V PC Signals.

But we are not getting the expected output.

Input to the Level shifter is fine.

Therefore, requesting you to verify the schematics and share your feedback on this issue.

Thanks & Regards,

Sai Ravali