Tool/software:

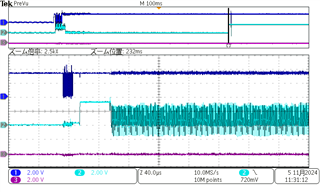

When we tested this IC, output waveform is sometimes oscillated. Would you see attached file?

In our application, pull-up/down register is not same condition.

This is not meet to the datasheet. Is this affected to the oscillation?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

When we tested this IC, output waveform is sometimes oscillated. Would you see attached file?

In our application, pull-up/down register is not same condition.

This is not meet to the datasheet. Is this affected to the oscillation?

Hello,

Similar to Clemens, can you please attach schematics and provide more detail (Input/Output) on the waveform. Thanks.

Regards,

Josh

The DIR input is referenced to VCCA; 3.3 V is not a valid signal level.

It is likely that the signal at pin 3 does not have a valid voltage either. (Please show the oscilloscope trace.) What is the purpose of the biasing circuit? Is this actually a digital signal?

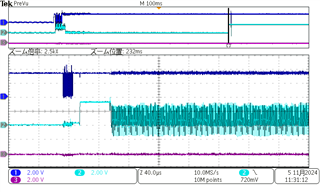

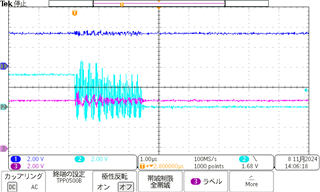

DIR input : I changed to 5Vpp signal. However, this oscillation issue still appered,

Would you see CH2 waveform of attached picture.

>What is the purpose of the biasing circuit? Is this actually a digital signal?

Based on requirement of Master device, this pull-up.down are mounted. This device detects function mode at power-up sequence by detecting pull-up or pull- down. These lines are data and clock of SPI signal.