Other Parts Discussed in Thread: TXV0108, TXB0304

Tool/software:

Hi Team,

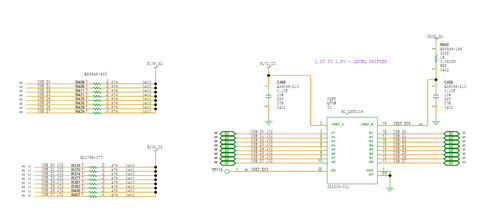

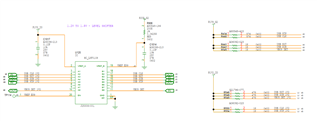

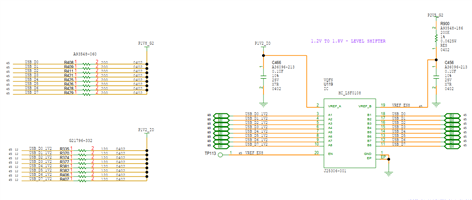

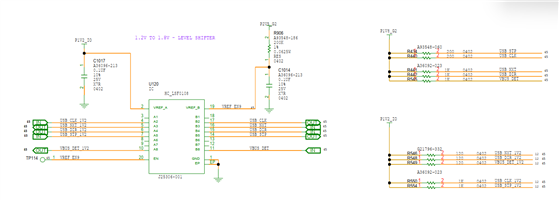

We are using LSF0108 in one of our designs to level translate signals between FPGA IO(1.2V) and USB3320

The max signal frequency is 60MHz and the data are bi-directional.

We have connected 2.5V to VREFB to maintain the BIAS Voltage

Could you let us know below circuitry is ok for the scenario mentioned

Thanks,

Rohini