Other Parts Discussed in Thread: ASH

Tool/software:

Hi,

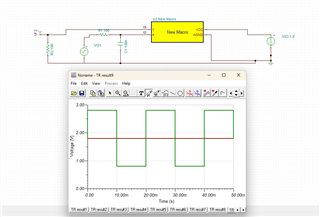

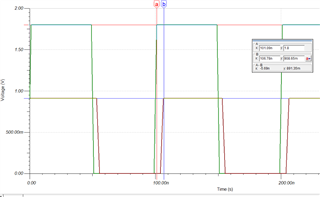

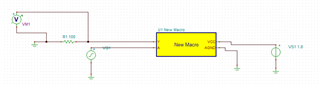

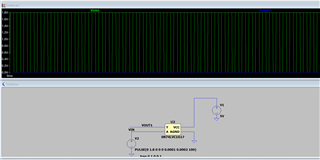

We are planning to use above part to provide delay upto 8ns. I am trying to do simulation but not able to see result as expected.

Any one can help me in simulation or let me know if any mistake in this below simulation.

Thanks

Ash