Dear TI,

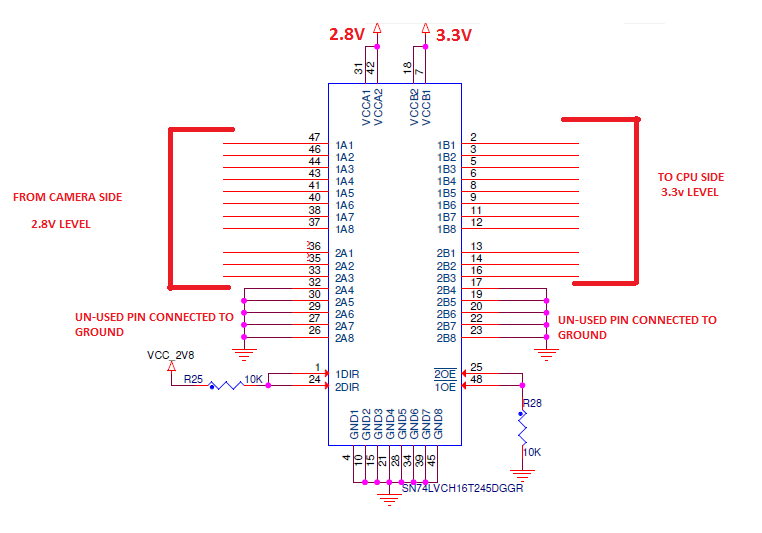

I'm using SN74LVCH16T245 for translating 2.8V camera signals to 3.3V camera signals. This IC has embedded with Bus-hold function.

1. Please let us know, how to enable and dis-enable the bus hold function.

2. Is it OK if I connected unused ins to ground ?

3. Please review the circuit diagram and share the feedback.

Regards,

Azlum