Other Parts Discussed in Thread: SN74AXC4T245, SN74AXC1T45

Hello,

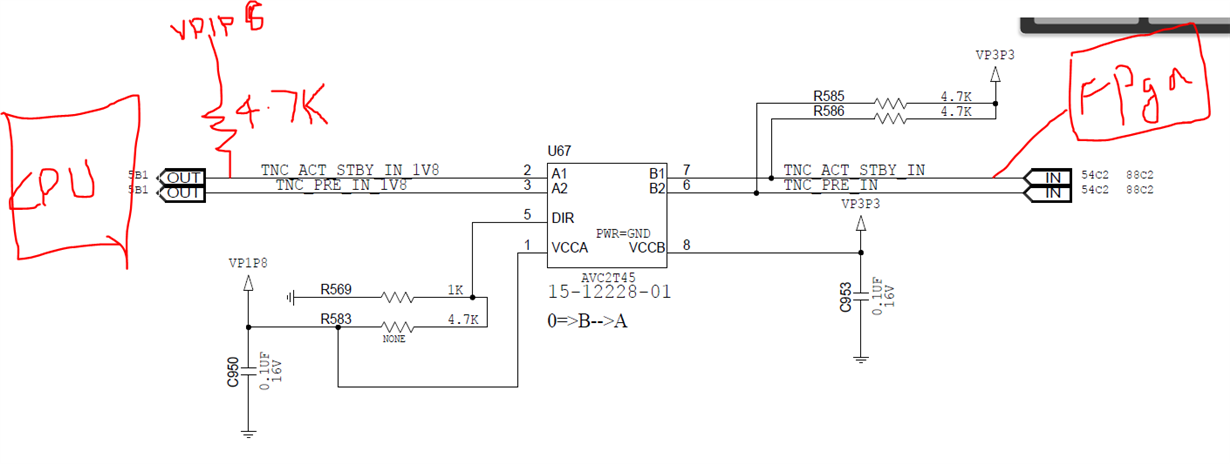

I have a query on the SN74AVC2t45 device. I understand from datasheet that when no vcca or vccb or both the I/o are in high impedance.

I am seeing a different behaviour in the implementation of our circuit. So, I would like to understand the reason. I am attaching the schema for reference.

There are 2 cards in our system which are connected by the control line through the buffer ( AVC2t45). The signal runs from card A to card B.

1. When we do power cycle of card A, we see that buffer output goes low immediately with 3.3V. Should it be holding high as we have the pull up on the card B?

2. How is the sink current getting the path when the 74AVC2t45 has a high impedance because the supplies are going down.

Let me know if I need to be clear on. I can give some more explanation.