Other Parts Discussed in Thread: TPL5110

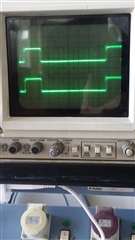

I'm designing a circuit in which the Q output of CD4047BM drives a MOSFET gate whose drain drives a relé coil, powered by a 1 F supercapacitor at 5 V; the CD4047BM is triggered by -TRIGGER input. During power on, with 5 V power supply voltage, a parasitic oscillation arises, also if the CD4047BM is still not triggered; the oscillation involves also the relé coil, and the vibration noise is heard. Oscilloscope measurements give 3 to 5 ms period of the produced oscillating square wave. Please, could you indicate how to avoid this? Thank you very much.