Other Parts Discussed in Thread: CD4040B, , TINA-TI, CD74HC4046A, SN74LV4046A

Hello,

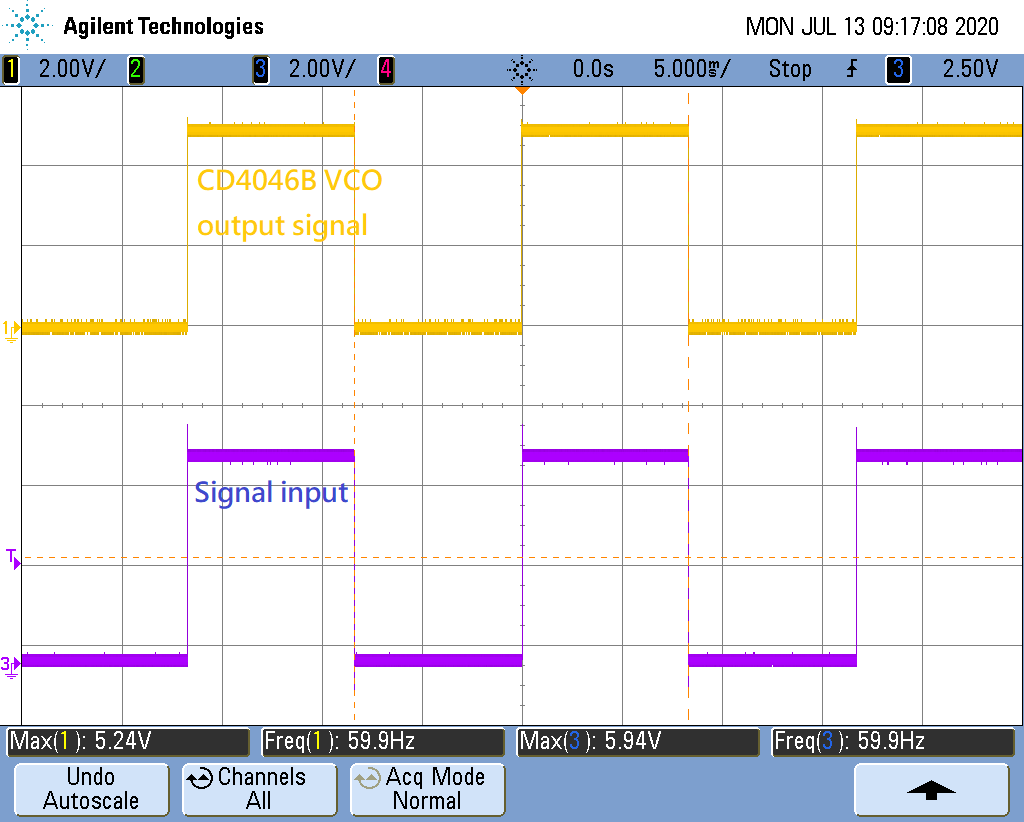

I would like to use PLL CD4046B and frequency divider CD4040B to design a 60Hz frequency locker.

The circuit target is to lock a 60Hz signal.

How could I start?

Please anyone to figure it out with me.

Thanks in advance.

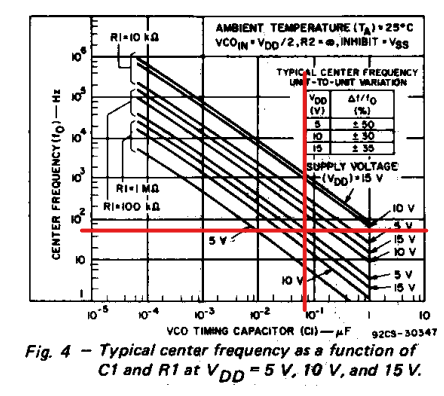

Assume that the VDD is 5VDC and only use the phase comparator 1, the frequency divider CD4040B can be divided by 1024 or 2048.

1. How to determine the VCO output frequency to achieve my target?

2. How to determine the value of R1, R2, C1, and low pass filter R3, C2?

3. Attached is the simulation file and the tool is LTSpice.

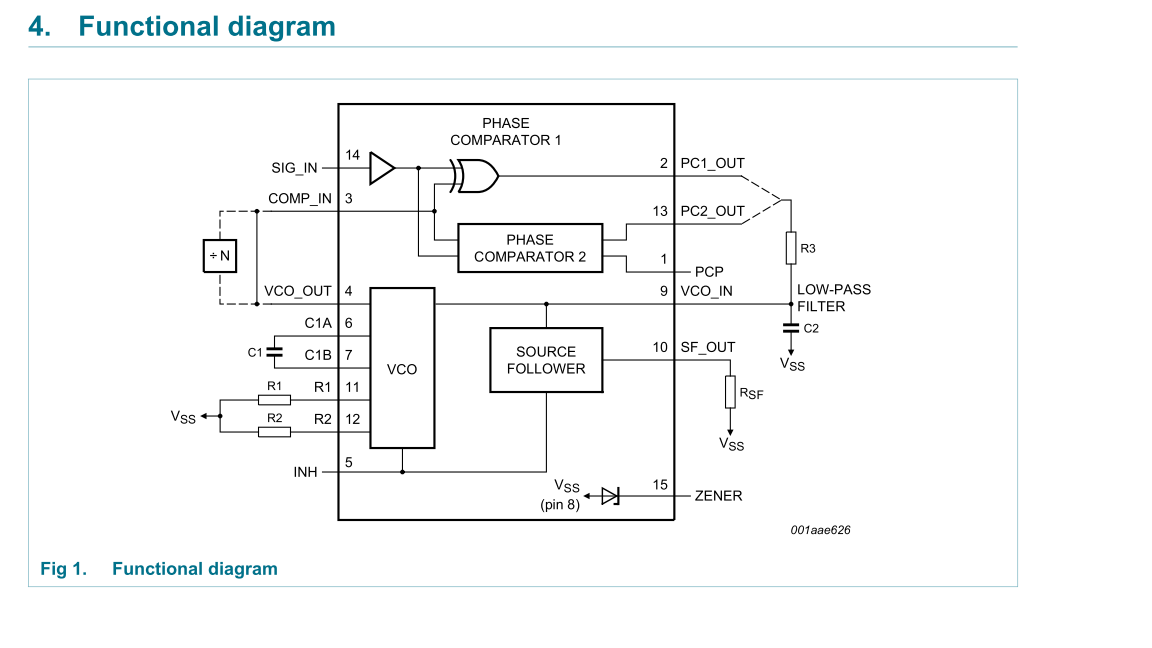

The detail can be find in HEF4046B datasheet.