Other Parts Discussed in Thread: SYSCONFIG

Hi,

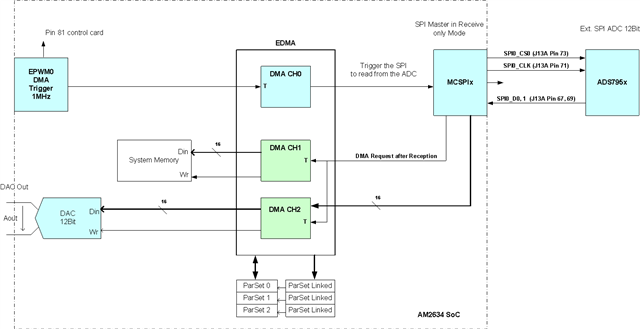

using the following setup I try to figure out how to configure the AM2634 SoC to receive serial data over SPI from an external ADC,

and to store those data in the system memory and for control purpose only I write it to the on Chip DAC port for verification.

- TI CCS Version: 11.2.0.00007

- SysConfig 1.14.0

- MCU SDK for AM263x Version: 8.5.0.24

The drawing below shall illustrate what I try to achieve:

Q: What is the best example I should look into in order to adapt it for the scenario shown above?

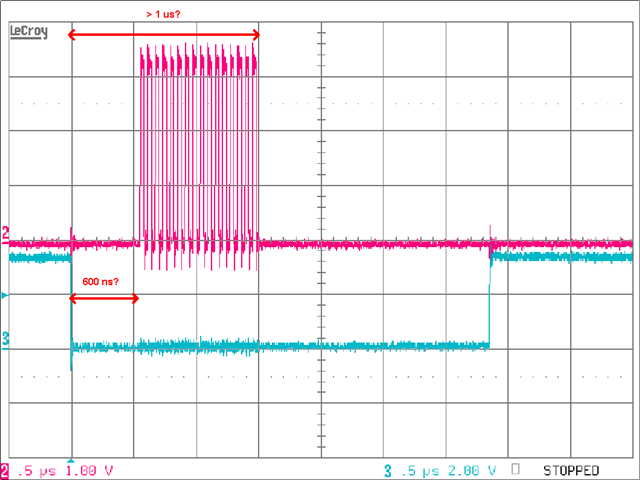

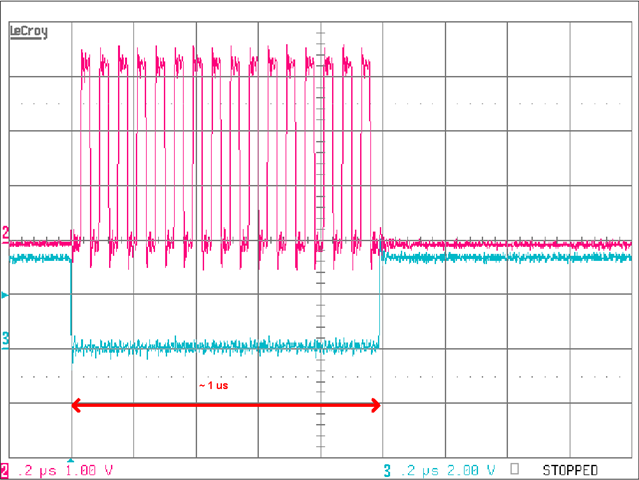

I tried to modify "mcspi_loopback_dma_am263x-cc_r5fss0-0_nortos_ti-arm-clang" within the SDK example section. However I am having troubles lowering

the SPI clock to 10MHz (in SysCfg). Doing so the example stops working. I am not sure if the current tool setup is actual enough to achieve what I want to

accomplish. I can measure the SPI_CLK it is being lowered to 10MHz. However it seems that the driver is somehow 'stuck' and never returns ...

Any hint would be appreciated

Markus