Part Number: TMS570LC4357

Hi team,

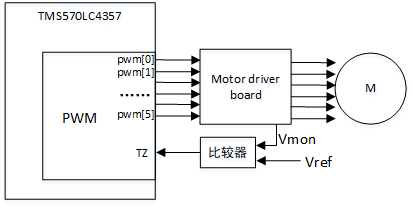

When driving a brushless three-phase motor with PWM, the motor drive board voltage is monitored using an analogue compare chip and connected to the TZ input of the PWM:

The signal is captured by an oscilloscope, and there are glitches on the signal that the analogue comparator outputs to the PWM TZ, and the glitch occurs in an unfixed position for each PWM cycle. The customer wants to filter the glitch on the TZ through the filtering function in the DC of the digital compare module in the PWM.

Assuming that T1 and T2 are two adjacent PWM periods (T2 is after the T1 time) in the figure below, as per the TMS570LC4357 PWM module DC section:

- The window counter begins counting after the offset counter counts down to 0

- Glitches in the window range are filtered

- The DCCAP register captures the time-base counter value when a DCEVFILT event occurs.

Based on the above premise, assuming that the glitch occurs in the middle of the TZ signal at T1 time, first the software needs to set the DC capture on and then read the value of the DCCAP register to set the offset length in the figure below with the value of the time base counter captured in DCCAP. The window range is also set according to the width of the glitch, so that the window filter range covers the area where the glitch occurs, for the purpose of filtering the glitch. However, if the location of the glitch on the TZ signal changes on the next cycle (T2 time), for example, the glitch occurs in the area after TZ, because the T1 time configured offsetn and window cannot meet the T2 time, resulting in the configured filter interval at T1 time to fail to filter the glitch at T2 time.

1) Does the DC filter glitch function in the PWM module only support filtering the glitches that are fixed on the TZ signal?

2) If the width of each glitch is different, how should software dynamically adjust the window counter value to cover the area where the glitch occurs?

Could you help check this case? Thanks.

Best Regards,

Cherry