Other Parts Discussed in Thread: SYSCONFIG

I want to configure multiple ADC channels to continuously read voltage and store the samples to RAM

The frequency of the sampling needs to be about 200Hz for all channels. For this reason, I want to use DMA.

I am trying to do proof-of-concept on the TI-TMDSCNCD263-AM263x Sitara Control Card.

It seems that the SDK example: adc_soc_continuous_dma_am263x-cc_r5fss0-0_nortos_ti-arm-clang.

I have this example working, but the SDK example fills the DMA buffers, and then stops. This is not what I want.

I want to modify example such that an application-layer event, at any time, can copy the DMA buffer to get a snapshot of the recent samples. Disabling interrupts momentarily, if needed, to copy the data is not a problem.

I experimented removing the function calls in the ISRs (seen here) which I suspected may be stopping the 'continuous ADC to DMA' that I want.

void App_adcISR(void *args)

{

/* Remove ePWM trigger */

EPWM_disableADCTrigger(CONFIG_EPWM0_BASE_ADDR, EPWM_SOC_A);

/* Disable this interrupt from happening again */

ADC_disableInterrupt(gAdc1baseAddr, ADC_INT_NUMBER1);

}

void App_dmach0ISR(Edma_IntrHandle intrHandle, void *args)

{

SemaphoreP_Object *semObjPtr = (SemaphoreP_Object *)args;

DebugP_assert(semObjPtr != NULL);

/* Stop the ADCs by removing the trigger for SOC0 */

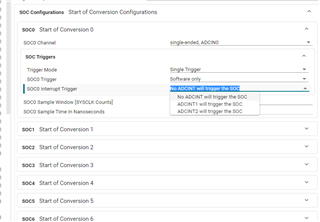

ADC_setInterruptSOCTrigger(gAdc1baseAddr, ADC_SOC_NUMBER0,

ADC_INT_SOC_TRIGGER_NONE);

ADC_setInterruptSOCTrigger(gAdc2baseAddr, ADC_SOC_NUMBER0,

ADC_INT_SOC_TRIGGER_NONE);

/* Post the semaphore to signal end of DMA transfer */

SemaphoreP_post(semObjPtr);

}

However, when I set a breakpoint in App_dmach0ISR() it only gets hit once.

Please advise on what needs to be done to achieve 'continuous ADC to DMA'.