Other Parts Discussed in Thread: AM2612, AM263P4

Tool/software:

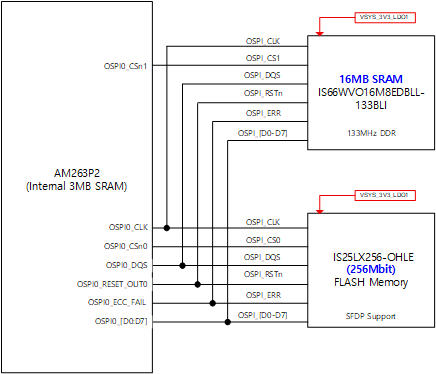

I'm planning to use the OSPI interface of the AM263P2 MCU as follows:

1. We plan to use the 16MB SRAM from ISSI for data logging via the OSPI interface CS1. (I understand this connection is slower than the SRAM inside the AM263P2, so I plan to use it for data reference purposes.)

- 133MB DDR CLK

- 3.3V power supply

2. We plan to use the 256Mbit flash memory from ISSI, which supports SFDP (Serial Flash Discoverable Parameters), via the OSPI interface CS0 for OS booting.

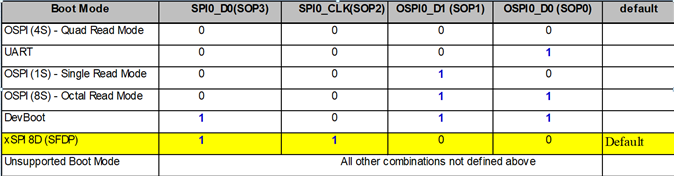

- MCU boot mode will be xSPI 8D (SFDP).

- 133MB DDR

- 3.3V power supply

3. We will use the OSPI signals in common, but use a separate chip select.

Question

1. Are there any issues with the circuit diagram?

2. Is there a problem with operating two components (SRAM and FLASH) simultaneously?