Hi people,

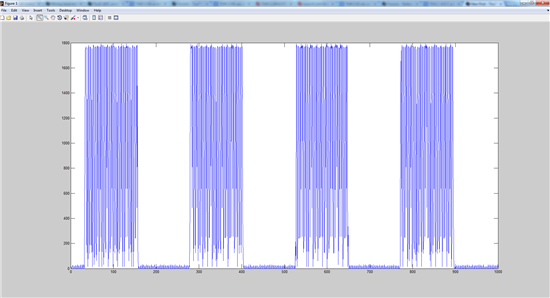

When digitalizing a 300 Hz square wave with a ADC triggered by a timer at 50 KHz, I don't get a pure square wave.. I have got a lot of glitches (several VCC to almost 0 transitions).

I am using a TIVA C TM4C1294XL evaluation kit.

The ADC is configured with a sequencer 3 and triggered by a 50000 Hz timer:

/**

* --------------------------------------------------------------------------

* Timer0

* --------------------------------------------------------------------------

*/

/* Configure the timer 0 as a 32-bit Timer in periodic mode. It combines timer 0A and

* Timer 0B (General Purpose Timer). TIMER0_BASE is the start of the timer registers for

* Timer0 in, the peripheral sectio nof the memory map.*/

TimerClockSourceSet(TIMER0_BASE, TIMER_CLOCK_SYSTEM);

TimerConfigure(TIMER0_BASE, TIMER_CFG_PERIODIC);

/*This function controls the ADC trigger output for the specified timer.

* If the bEnable parameter is true, then the timer’s ADC output trigger is enabled;

* otherwise it is disabled.*/

TimerControlTrigger(TIMER0_BASE, TIMER_A, true);

// Maintain this disabled!

TimerLoadSet(TIMER0_BASE, TIMER_A, (ui32SysClkFreq / (ap.ac_signal_frequency)) / 2 - 1);

TimerDisable(TIMER0_BASE, TIMER_A);

// Middle priority

IntPrioritySet(INT_TIMER0A, 1);

The ADC initialization code after the clocks and gpios configuration is:

/**

* --------------------------------------------------------------------------

* ADC

* --------------------------------------------------------------------------

*/

/* ADC 0 - Disable */

ADCSequenceDisable(ADC0_BASE, 3);

/* ADC 1 - Disable */

//ADCSequenceDisable(ADC1_BASE, 3);

/* ADC0 - Sample Sequencer 1 - Timer Trigger the Sampling and Highest Priority*/

ADCSequenceConfigure(ADC0_BASE, 3, ADC_TRIGGER_TIMER, 0);

/* ADC1 - Sample Sequencer 1 - Timer Trigger the Sampling and Highest Priority*/

//ADCSequenceConfigure(ADC1_BASE, 3, ADC_TRIGGER_TIMER, 0);

/* ADC 0 - ADC_CTL_TS is the channel linked to the CH1*/

ADCSequenceStepConfigure(ADC0_BASE, 3, 0, ADC_CTL_CH1 | ADC_CTL_SHOLD_4 |ADC_CTL_IE |ADC_CTL_END);

/* ADC 1 - ADC_CTL_TS is the channel linked to the CH1*/

//ADCSequenceStepConfigure(ADC1_BASE, 3, 0, ADC_CTL_CH2 |ADC_CTL_IE |ADC_CTL_END);

/* ADC 0 - Enable the ADC sequencer 1.*/

ADCSequenceEnable(ADC0_BASE, 3);

/* ADC 1 - Enable the ADC sequencer 1.*/

//ADCSequenceEnable(ADC1_BASE, 3);

/* ADC 0 - Enables the specific vector associated with ADC0_BASE.*/

IntEnable(INT_ADC0SS3);

/* ADC 1 - Enables the specific vector associated with ADC1_BASE.*/

//IntEnable(INT_ADC1SS3);

/* ADC 0 - Enables a specific event*/

ADCIntEnable(ADC0_BASE, 3);

/* ADC 1 - Enables a specific event*/

//ADCIntEnable(ADC1_BASE, 3);

The ADC ISR code is:

/**

* \brief This function utilizes the ADC ISR to acquire samples from the ADC.

* @param void :

* @return void :

*/

void ADC0IntHandler(void)

{

uint32_t ui32ADC0Value;

/* ADC 0 - Clear the INterrupt Flag*/

ADCIntClear(ADC0_BASE, 3);

/* Disable Timer */

TimerDisable(TIMER0_BASE, TIMER_A);

/* ADC 0 - Get the data */

ADCSequenceDataGet(ADC0_BASE, 3, &ui32ADC0Value);

/* ADC 0 - Un-pend an interrupt */

IntPendClear(INT_ADC0SS3);

ram_store_b1[sf.nsamples_bridge1] = ui32ADC0Value;

sf.nsamples_bridge1++;

if(sf.nsamples_bridge1 >= ap.maximum_nsamples ) //&& sf.nsamples_bridge2 >= ap.maximum_nsamples)

{

sf.machine_state = MEASURE_COMPLETE_STATE;

}

else

{

/* Enable the timer */

//TimerLoadSet(TIMER0_BASE, TIMER_A, (ui32SysClkFreq / (ap.ac_signal_frequency)) / 2 - 1);

TimerEnable(TIMER0_BASE, TIMER_A);

}

}

Thank you.