Hi All,

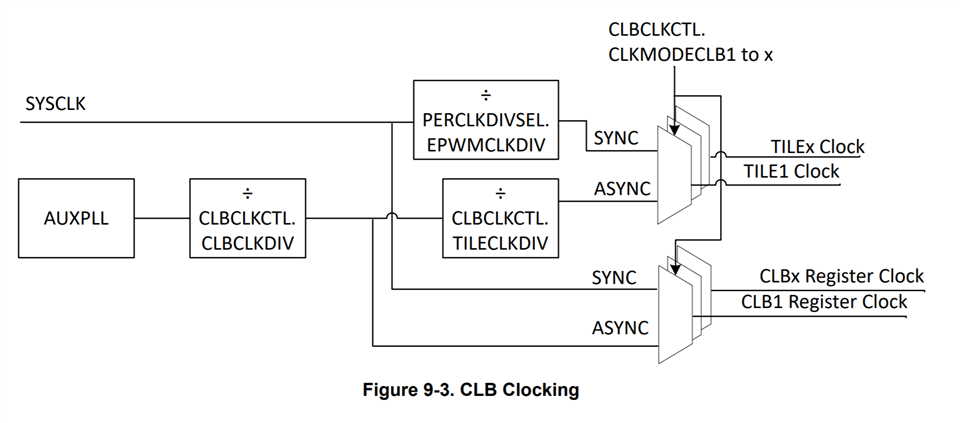

It is mentioned that the CLB clock is derived either from SYSCLK or AUXPLL, but I do not see the mention of CLB in the main clock diagram. Can you provide an updated diagram for this? Is it correct to assume the SYSCLK is CPUx.SYSCLK and AUXPLL is AUXPLLRAWCLK (that goes as input for ETHERCAT and CM)?

Also it is mentioned that maximum frequency for CLB clock is 150 Mhz. Does this mean that we need to ensure the 150 Mhz for CLB tile clock and register clock by setting the appropriate dividers (EPWMCLKDIV or CLBCLKDIV/TILECLKDIV) when SYSCL /AUXPLL is > 150 Mhz ?

Any specific reason on why EPWMCLKDIV is applicable when used in SYNC mode and not CLBCLKDIV/TILECLKDIV?

Also in the following diagram, when you refer CLB clock are you referring to tile clock or register clock?

Thanks,

Aditya