Dear C2000 expert,

When I testing some of abnormal situation for pmbus slave mode, I found that the CLK_HIGH_DETECTED in PMBSTS won't get set. Can you please help me know why?

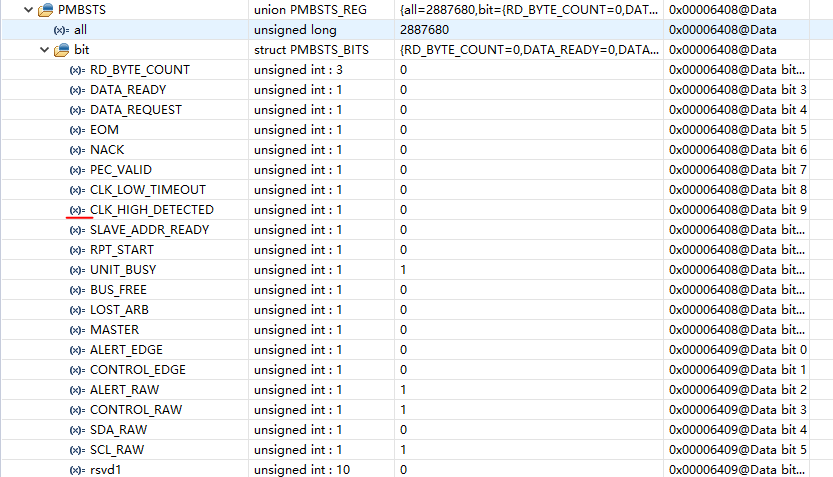

My testing condition is that master read block data from slaver, and I made master hold the clock high after reading one byte (not finish reading all bytes). This is abnormal condition for master. But in this condition, I found that CLK_HIGH_DETECTED in PMBSTS won't get set. Please see below picture that capture PMBSTS value via CCS.

Please see my testing waveform as below, the first waveform show that the master hold the clock to high but not finished all reading bytes, slave pull down data line to low. The second waveform shows the last byte that master read from slaver before enter into abnormal situation.

Our customer systems require that the slaver have to recover to normal state(clk and data release to idle) once detecting any of abnormal situation happens including master. Can you share some suggestion in this case? Thanks...

My initialized code for PMBus:

pmbus_base = PMBUSA_BASE;

pmbus_slave_addr = 0x58u;

PMBus_initSlaveMode(pmbus_base,pmbus_slave_addr,0x7fu);

PMBus_configSlave(pmbus_base,PMBUS_PMBSC_PEC_ENA|PMBUS_PMBSC_RX_BYTE_ACK_CNT_M);

/* Configure the PMBUS module clock to be PMBUS_MODULE_FREQ_MAX */

uint32_t moduleFreq = PMBus_configModuleClock(PMBUSA_BASE, (PMBUS_MODULE_FREQ_MAX>>1), PMBUS_SYS_FREQ_MAX);

/* Configure the PMBUS bus clock */

PMBus_configBusClock(PMBUSA_BASE, PMBUS_CLOCKMODE_STANDARD, moduleFreq);

Regards,

Jack