Other Parts Discussed in Thread: C2000WARE

i have a question regarding the DCC counters configuration :

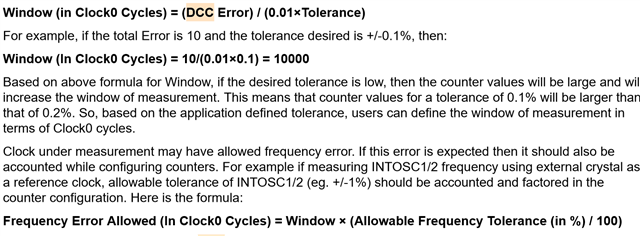

- Procedure I followed is from page number 63 from Reference manual tms320f28002 and here are some calculations :

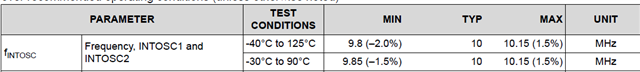

PLL frequency 100MHz that is clock1

Clock0 10MHz

Both Tolerance is 1 % then I have the following counter values

DCC error : 30

Window : 3000

Frequency error allowed 30

Total error 3030

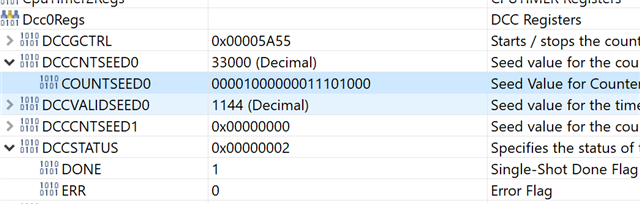

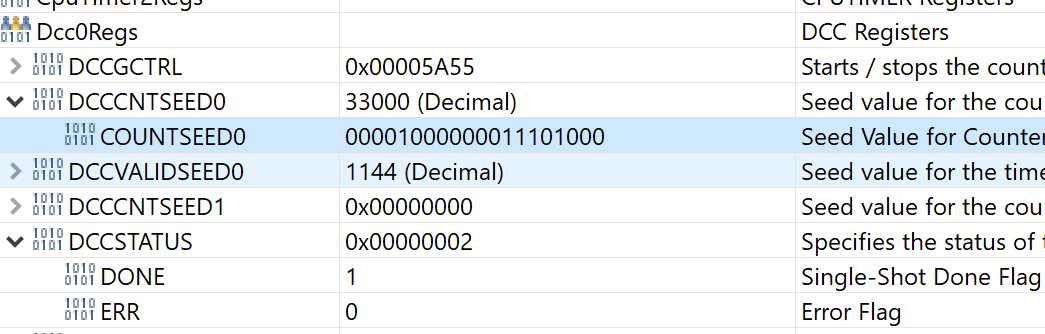

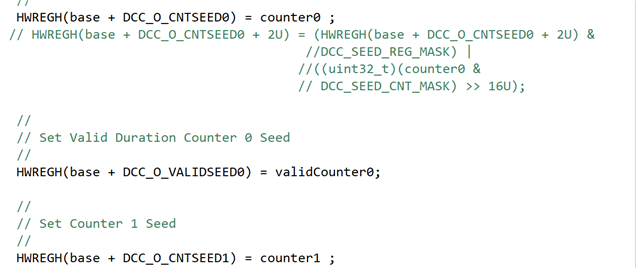

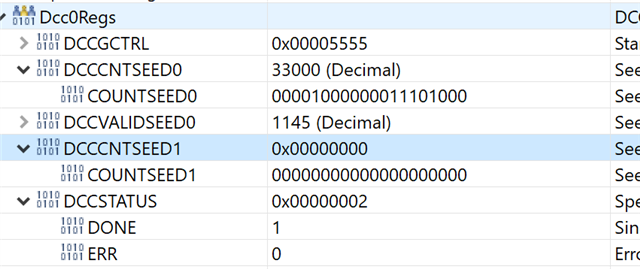

Counter0 : 30

Counter1:30000

Valid0 : 2*3030 :6060

In this case : error detection time is around 600us and test time is 300us

- Procedure taken from Continuous Monitor of the PLL Frequency With the DCC from example calculation

PLL frequency : 100MHz

Clk0 : 10 MHz

Resolution 0,1%

Valid min : 10

Counter1: 50000

Counter0 : 499,5

Could you please tell me why there are two procedures ?