Other Parts Discussed in Thread: C2000WARE

Hi Expert,

My customer use updown mode for generating HRPWM, they do the modification from the below example, they do the AQ configuration as below, and found that duty cycle for PWM1B is correct, but there is some problem for PWM1A.

C:\ti\c2000\C2000Ware_3_02_00_00\device_support\f28004x\examples\hrpwm

EPWM_setActionQualifierAction(EPWM1_BASE, EPWM_AQ_OUTPUT_A,

EPWM_AQ_OUTPUT_HIGH,

EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPA);

EPWM_setActionQualifierAction(EPWM1_BASE, EPWM_AQ_OUTPUT_A,

EPWM_AQ_OUTPUT_LOW,

EPWM_AQ_OUTPUT_ON_TIMEBASE_PERIOD);

// EPWM_setActionQualifierAction(EPWM1_BASE, EPWM_AQ_OUTPUT_B,

// EPWM_AQ_OUTPUT_LOW,

// EPWM_AQ_OUTPUT_ON_TIMEBASE_PERIOD);

EPWM_setActionQualifierAction(EPWM1_BASE, EPWM_AQ_OUTPUT_B,

EPWM_AQ_OUTPUT_HIGH,

EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPB);

EPWM_setActionQualifierAction(EPWM1_BASE, EPWM_AQ_OUTPUT_B,

EPWM_AQ_OUTPUT_LOW,

EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO);

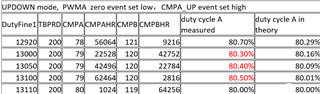

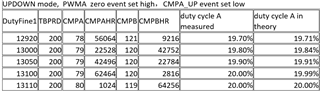

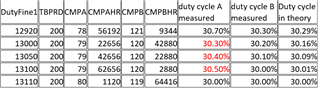

they do the test to get the relationship between the output duty cycle and CMPA, CMPAHR as below, and the duty cycle for PWM1A is not correct as the red mark.

when CMPA increase from 78 to 80, the duty cycle decreased which is correct as expected.

but when CMPA is 79, as CMPAHR value increase, the duty cycle measured is also increased, which is not correct as expected,

Any suggestion for this? I post the code here for more details.

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/171/Code_5F00_test.7z