Part Number: TMDSCNCD28379D

Other Parts Discussed in Thread: C2000WARE

Hi,

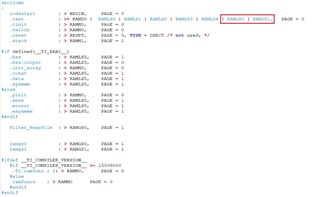

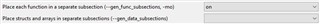

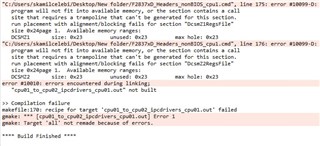

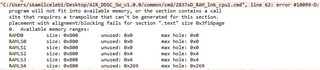

I am getting the errors in the picture below in my project.

Project compiler console output is below.

How can i bug these errors? I am waiting for your help.

Best regards,

Thanks,

Good days.