Hi champs,

AMC1306 outputs data at clock rising edge, normally we should invert C2000 device’s SDFM clock pin so that SDFM receives data from AMC1306 at clock falling edge.

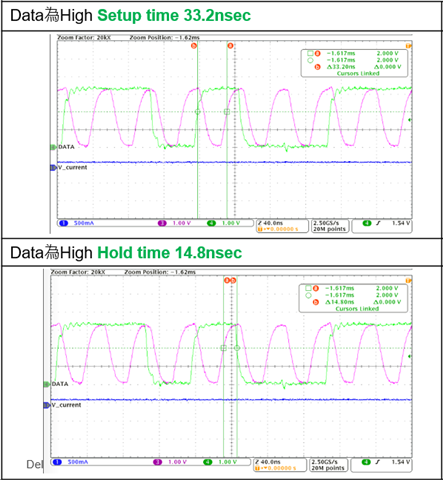

My customer doesn’t invert SDFM clock pin and conducts one experiment, the result is not good for sure. He captures the SDFM waveform and would like to understand the details, please refer to below picture. It seems that the setup and hold time for SDFM clock is enough(3-sample, 10ns) and the data just shift one bit, means that 1st clock catches wrong data, 2nd clock catches 1st data, third clock catches 2nd data, and so on.

Since the waveform looks good for SDFM module to receive data, my customer wants to know the reason he gets bad SDFM data result if not invert SDFM clock pin for data receiving. Please advise your comments on this question, thanks for help.

Regards,

Luke