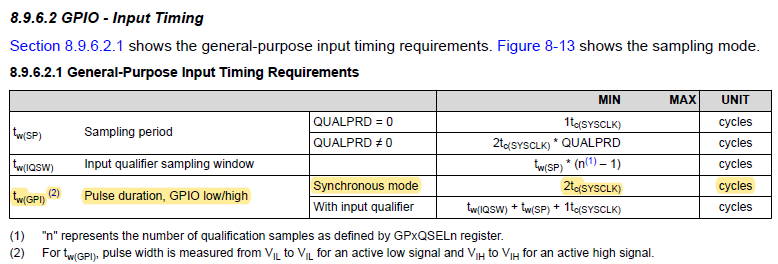

I was trying to figure out the GPIO input speed limitations but cant find it in the datasheet. I see OUTPUT TIMING in section 8.9.6.1 and wanted that same information about the input. Is there another document that has this information?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.