Other Parts Discussed in Thread: DAC7578, TCA9555, C2000WARE

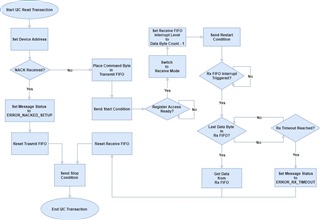

Hello, I'm working on the I2C Transactions for my system and I've noticed that in order to get my transactions to complete safely I need a delay of about 75us between each transaction in order for everything to finish properly with a Stop Condition. At a delay of about 60us or less I start to lose bus stability with bytes from previous transactions appearing in the next transaction, Missed Stop Conditions, and/or ultimately locking up the bus entirely. Is there anyone that might have any insight as to why that might be happening? With the Delay everything runs smoothly but I would like to reduce this amount of delay if possible.

Thank You!