Hi champs,

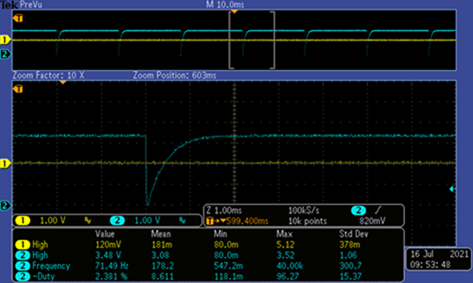

My customer implements one EtherCAT firmware upgrade function, means that F28388D receives software image via EtherCAT and then do flash programming. But after he finish CPU1 upgrade, F28388D fails to boot up and outputs a low signal to XRS pin periodically, please refer to below pictures.

This waveform looks like watchdog reset is happening, but the strange thing is that we don't see 512 OSCCLK(51.2us) low period. My customer cannot connect F28388D via JTAG port with correct password, then he sets SCI Boot(GPIO72 = 0, GPIO84 = 1), power cycle his system and get same result, F28388D outputs a low signal to XRS pin periodically.

It seems that GPIO72 and GPIO84 cannot force F28388D to do SCI_Boot, I know User OTP can change boot mode GPIO pins, but my customer didn't do that.

Please advise your comments if any, how to do further check and recognize what's wrong with this F28388D?

Thanks and regards,

Luke