Dear team:

When using the PWM phase shift function, my customer found that setting TBPHS equal to CMPA would cause the CMPA event to be lost. Details are as follows:

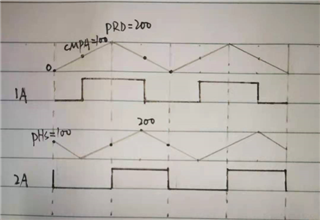

PWM1: UP_DOWN mode, fixed 50% duty cycle, SET for CMPA_U, CLR for CMPA_D, and a synchronization signal when CTR=0;

PWM2: UP_DOWN mode, fixed 50% duty cycle, SET for CMPA_U, CLR for CMPA_D;

PWM2 performs phase shift on the basis of PWM1, and the phase shift value is in the range of 0~PRD. The schematic diagram is as follows:

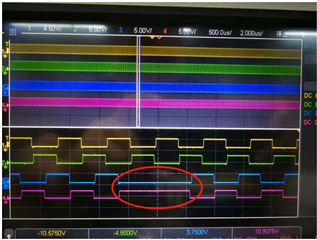

The problem now is that when the TBPHS value is close to the CMPA value (for example, CMPA=100, PHS=99/100/101), the waveform sent by PWM2 will be lost. The situation is shown in the figure below:

May I ask what causes it? What needs to be done?