Other Parts Discussed in Thread: SN65HVD485E,

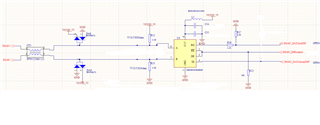

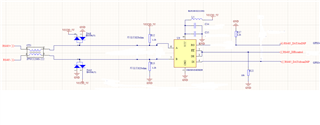

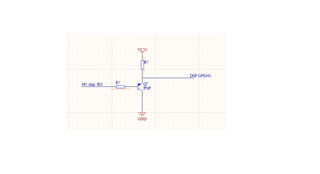

I use 28069M SCIB module to implement RS485 communication with a encoder based on modbus-rtu protocol. The 28069M board is customized. The 485chip is SN65HVD485.

GPIO40 is configured as SCITXDB;

GPIO41 is configured as SCIRXDB;

GPIO43 is configured as direction control;

MCU is as master, encoder is as slave.

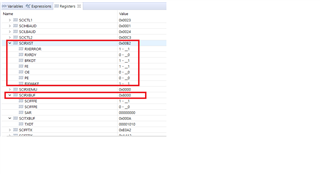

SCIB transmitter interrupt and receiver interrupt are all enabled;

The transmitter buffer and receiver buffer level =2;

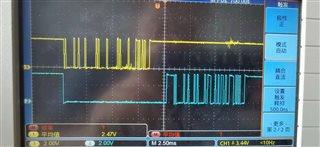

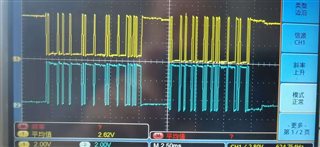

The current situation is that MCU transmitter seems ok because the encoder returned pulses out (If the transmitted pulses to encoder is not correct, then the encoder will not return out pulses).

But the receiver displays errors as below in CCS debug window:

Since the error generated, the receive interrupt can not be entered.

How to solve that ? Any comment will be appreciated.