Other Parts Discussed in Thread: C2000WARE, TMDSCNCD28379D

Hi,

I want to generate 20 MHz SPI CLK frequency. I am doing the calculation as follows.

// // Calculate BRR: 7-bit baud rate register value // SPI CLK freq = 500 kHz // LSPCLK freq = CPU freq / 4 (by default) // BRR = (LSPCLK freq / SPI CLK freq) - 1 // #if CPU_FRQ_200MHZ #define SPI_BRR ((200E6 / 4) / 20E6) - 1 // 20MHz CLK Signal. #endif

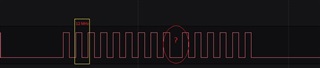

However, when I look at the signal with the logic analyzer, the CLK signal looks wrong. I marked the CLK signal output picture with yellow and red lines.

Yellow line in the image = SPI CLK signal is 12 MHz.

Red line in the image = 8 MHz field.

I am using the example below.

C:\ti\c2000\C2000Ware_3_04_00_00\device_support\f2837xd\examples\cpu1\spi_loopback

Is there an error in the calculation process?

Sinan,

Thanks and Best regards.