Other Parts Discussed in Thread: TMS320F28377D

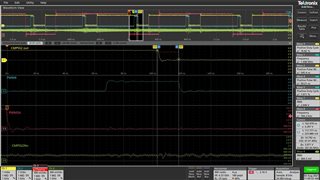

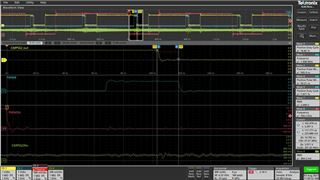

CMPSS2 was set to ramp and reset with PWM4’s CMPC, which in this case was set to 5 (CMPA was also set to five and controls where the falling edge of PWM4 occurs, so the comparator should be resetting every falling edge of PWM4). We noticed it will reset about 15ns early each cycle. We observed this with the same settings as issues 1 and 2 (link). We observed this issue on both the TMS320F28379D eval card and on custom hardware using a TMS320F28377D. The input to CMPSS2+ was 0.360V. The microcontroller was clocked at 20MHz with the PLL configured to produce a system clock of 200MHz, and the PWM clock was set to 100MHz.

Minimal working code is attached1222.minimal_working_example.zip