Hi,

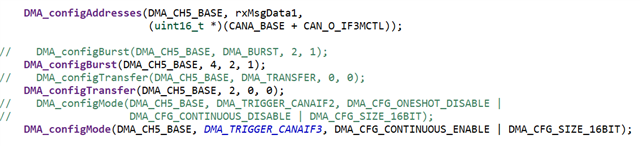

I am using IF3 registers with DMA mode. My program configuration is as follow(based on "can_ex4_loopback_dma"):

1. The DMA src Addr is CAN_IF3MCTL, and I want to move 2 words with DMA. It will move the value of CAN_IF3MCTL and CAN_IF3DATA register to the Custom array "rxMsgData1[4]" ideally.

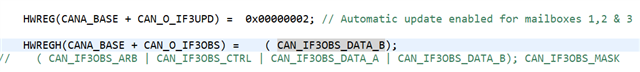

2. For testing, I only set Data_B bit in CAN_IF3OBS Register.

3.The result is as follow:

CAN_IF3MCTL and CAN_IF3DATA register get the true value, and the Custom array "rxMsgData1[4]" also get the true value by DMA.

QUESTION:

1.But what surprised me was that I only set Data_B bit in CAN_IF3OBS Register. I didn't set Data_A bit or Ctrl bit in CAN_IF3OBS Register at all. Why?

2.IF I want to use IF3 registers with DMA mode, how can I configure the CAN_IF3OBS Register and related registers of DMA?